求助大侠 神经网络无法仿真

时间:10-02

整理:3721RD

点击:

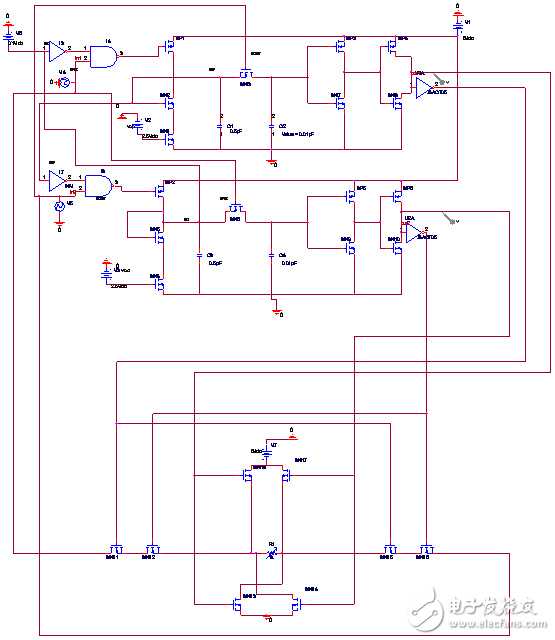

用数字电路仿真神经网络 但无法仿真

** Creating circuit file "ep-schematic1-000.sim.cir"

** WARNING: THIS AUTOMATICALLY GENERATED FILE MAY BE OVERWRITTEN BY SUBSEQUENT SIMULATIONS

*Libraries:

* Local Libraries :

* From [PSPICE NETLIST] section of C:\Program Files\Orcad\PSpice\PSpice.ini file:

.lib "nom.lib"

*Analysis directives:

.TRAN 0 200ms 0

.PROBE V(*) I(*) W(*) D(*) NOISE(*)

.INC ".\ep-SCHEMATIC1.net"

**** INCLUDING ep-SCHEMATIC1.net ****

* source EP

M_MP1 N00719 N00527 N00654 N00654 MbreakP

X_I4 N00465 IN1 N00527 $G_DPWR $G_DGND NAN2

M_MN8 OUT1 N00907 0 0 MbreakN

M_MN16 N74804 N78662 IN2 IN2 MbreakN

M_MN13 N74771 OUT1 0 0 MbreakN

M_MN15 N74771 N78641 N74804 N74804 MbreakN

M_MN10 OUT2 N19721 0 0 MbreakN

X_I8 N19242 IN2 N19423 $G_DPWR $G_DGND NAN2

M_MP2 N19546 N19423 N00654 N00654 MbreakP

M_MN2 N00719 N00719 N17924 N17924 MbreakN

M_MN1 N17924 N21991 0 0 MbreakN

M_MN18 N74983 OUT1 N74615 N74615 MbreakN

M_MN12 N89744 N78662 N74615 N74615 MbreakN

M_MP3 N00907 N01006 N00654 N00654 MbreakP

R_R1 N74615 N74771 {1k*0.5+.001}

M_MN14 N74615 OUT2 0 0 MbreakN

C_C1 0 N00719 0.5pF

M_MN3 N01006 IN2 N00719 N00719 MbreakN

X_I3 N19546 N00465 $G_DPWR $G_DGND INV

M_MN5 N19546 N19546 N19590 N19590 MbreakN

V_V2 N21991 0 2.5Vdc

C_C2 0 N01006 0.01pF

V_V1 N00654 0 5Vdc

M_MP4 OUT1 N00907 N00654 N00654 MbreakP

C_C3 0 N19546 0.5pF

M_MN7 N00907 N01006 0 0 MbreakN

M_MP5 N19721 N19887 N00654 N00654 MbreakP

X_U1A OUT1 N78641 $G_DPWR $G_DGND 74ACT05 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

C_C4 0 N19887 0.01pF

V_V7 0 N74983 5Vdc

M_MN9 N19721 N19887 0 0 MbreakN

X_I7 N00719 N19242 $G_DPWR $G_DGND INV

M_MP6 OUT2 N19721 N00654 N00654 MbreakP

V_V4 IN1 0

+PWL 0ms 0V 4.999ms 0V 5ms 1.2V 5.1ms 1.2V 5.101ms 0V 59.999ms 0V 60ms 1.2V

+ 60.1ms 1.2V 60.101ms 0V

M_MN6 N19887 IN1 N19546 N19546 MbreakN

M_MN17 N74983 OUT2 N74771 N74771 MbreakN

V_V5 IN2 0

+PWL 0ms 0V 5.999ms 0V 6ms 1.2V 6.1ms 1.2V 6.101ms 0 74.999ms 0V 75ms 1.2V

+ 75.1ms 1.2V 75.101ms 0V

M_MN11 IN1 N78641 N89744 N89744 MbreakN

V_V3 N24451 0 2.5Vdc

M_MN4 N19590 N24451 0 0 MbreakN

V_V6 N19546 0 0.1Vdc

X_U2A OUT2 N78662 $G_DPWR $G_DGND 74ACT05 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

**** RESUMING ep-schematic1-000.sim.cir ****

.END

**** Generated AtoD and DtoA Interfaces ****

*

* Analog/Digital interface for node N00719

*

* Moving X_I7.U1:IN1 from analog node N00719 to new digital node N00719$AtoD

X$N00719_AtoD1

+ N00719

+ N00719$AtoD

+ $G_DPWR

+ $G_DGND

+ AtoDdefault

+ PARAMS: CAPACITANCE= 0

*

* Analog/Digital interface for node N00527

*

* Moving X_I4.U1:OUT1 from analog node N00527 to new digital node N00527$DtoA

X$N00527_DtoA1

+ N00527$DtoA

+ N00527

+ $G_DPWR

+ $G_DGND

+ DtoAdefault

+ PARAMS: DRVH= 50 DRVL= 50 CAPACITANCE= 0

*

* Analog/Digital interface for node OUT1

*

* Moving X_U1A.U1:IN1 from analog node OUT1 to new digital node OUT1$AtoD

X$OUT1_AtoD1

+ OUT1

+ OUT1$AtoD

+ $G_DPWR

+ $G_DGND

+ AtoD_ACT

+ PARAMS: CAPACITANCE= 5.0000E-12

*

* Analog/Digital interface for node N78662

*

* Moving X_U2A.U1:OUT1 from analog node N78662 to new digital node N78662$DtoA

X$N78662_DtoA1

+ N78662$DtoA

+ N78662

+ $G_DPWR

+ $G_DGND

+ DtoA_AC_OC

+ PARAMS: DRVH= 1.0000E+06 DRVL= 18.7 CAPACITANCE= 0

*

* Analog/Digital interface for node IN2

*

* Moving X_I8.U1:IN2 from analog node IN2 to new digital node IN2$AtoD

X$IN2_AtoD1

+ IN2

+ IN2$AtoD

+ $G_DPWR

+ $G_DGND

+ AtoDdefault

+ PARAMS: CAPACITANCE= 0

*

* Analog/Digital interface for node N78641

*

* Moving X_U1A.U1:OUT1 from analog node N78641 to new digital node N78641$DtoA

X$N78641_DtoA1

+ N78641$DtoA

+ N78641

+ $G_DPWR

+ $G_DGND

+ DtoA_AC_OC

+ PARAMS: DRVH= 1.0000E+06 DRVL= 18.7 CAPACITANCE= 0

*

* Analog/Digital interface for node OUT2

*

* Moving X_U2A.U1:IN1 from analog node OUT2 to new digital node OUT2$AtoD

X$OUT2_AtoD1

+ OUT2

+ OUT2$AtoD

+ $G_DPWR

+ $G_DGND

+ AtoD_ACT

+ PARAMS: CAPACITANCE= 5.0000E-12

*

* Analog/Digital interface for node N19546

*

* Moving X_I3.U1:IN1 from analog node N19546 to new digital node N19546$AtoD

X$N19546_AtoD1

+ N19546

+ N19546$AtoD

+ $G_DPWR

+ $G_DGND

+ AtoDdefault

+ PARAMS: CAPACITANCE= 0

*

* Analog/Digital interface for node N19423

*

* Moving X_I8.U1:OUT1 from analog node N19423 to new digital node N19423$DtoA

X$N19423_DtoA1

+ N19423$DtoA

+ N19423

+ $G_DPWR

+ $G_DGND

+ DtoAdefault

+ PARAMS: DRVH= 50 DRVL= 50 CAPACITANCE= 0

*

* Analog/Digital interface for node IN1

*

* Moving X_I4.U1:IN2 from analog node IN1 to new digital node IN1$AtoD

X$IN1_AtoD1

+ IN1

+ IN1$AtoD

+ $G_DPWR

+ $G_DGND

+ AtoDdefault

+ PARAMS: CAPACITANCE= 0

*

* Analog/Digital interface power supply subcircuits

*

X$DIGIFPWR 0 DIGIFPWR

**** 05/26/15 16:00:43 ********* PSpice 9.2 (Mar 2000) ******** ID# 1 ********

** Profile: "SCHEMATIC1-000" [ D:\LTD\ep-schematic1-000.sim ]

**** MOSFET MODEL PARAMETERS

******************************************************************************

MbreakP MbreakN

PMOS NMOS

LEVEL 1 1

L 100.000000E-06 100.000000E-06

W 100.000000E-06 100.000000E-06

VTO 0 0

KP 20.000000E-06 20.000000E-06

GAMMA 0 0

PHI .6 .6

LAMBDA 0 0

IS 10.000000E-15 10.000000E-15

JS 0 0

PB .8 .8

PBSW .8 .8

CJ 0 0

CJSW 0 0

CGSO 0 0

CGDO 0 0

CGBO 0 0

TOX 0 0

XJ 0 0

UCRIT 10.000000E+03 10.000000E+03

DIOMOD 1 1

VFB 0 0

LETA 0 0

WETA 0 0

U0 0 0

TEMP 0 0

VDD 0 0

XPART 0 0

**** 05/26/15 16:00:43 ********* PSpice 9.2 (Mar 2000) ******** ID# 1 ********

** Profile: "SCHEMATIC1-000" [ D:\LTD\ep-schematic1-000.sim ]

**** Digital Input MODEL PARAMETERS

******************************************************************************

DIN74 DIN74AC_OC

FILE DSO_DTOA DSO_DTOA

FORMAT 6 6

TIMESTEP 100.000000E-12 100.000000E-12

S0NAME 0 0

S0TSW 3.500000E-09 700.000000E-12

S0RLO 7.13 1

S0RHI 389 100.000000E+03

S1NAME 1 1

S1TSW 5.500000E-09 700.000000E-12

S1RLO 467 200.000000E+03

S1RHI 200 200.000000E+03

S2NAME X X

S2TSW 3.500000E-09 700.000000E-12

S2RLO 42.9 104

S2RHI 116 100

S3NAME R R

S3TSW 3.500000E-09 700.000000E-12

S3RLO 42.9 104

S3RHI 116 100

S4NAME F F

S4TSW 3.500000E-09 700.000000E-12

S4RLO 42.9 104

S4RHI 116 100

S5NAME Z Z

S5TSW 3.500000E-09 700.000000E-12

S5RLO 200.000000E+03 200.000000E+03

S5RHI 200.000000E+03 200.000000E+03

**** 05/26/15 16:00:43 ********* PSpice 9.2 (Mar 2000) ******** ID# 1 ********

** Profile: "SCHEMATIC1-000" [ D:\LTD\ep-schematic1-000.sim ]

**** Digital Output MODEL PARAMETERS

******************************************************************************

DO74 DO74ACT

FILE DSO_ATOD DSO_ATOD

FORMAT 6 6

CHGONLY 1 1

TIMESTEP 100.000000E-12 100.000000E-12

S0NAME X X

S0VHI 2 2

S0VLO .8 .8

S1NAME 0 0

S1VHI .8 .8

S1VLO -1.5 -1.5

S2NAME R R

S2VHI 1.4 1.55

S2VLO .8 .8

S3NAME R R

S3VHI 2 2

S3VLO 1.3 1.45

S4NAME X X

S4VHI 2 2

S4VLO .8 .8

S5NAME 1 1

S5VHI 7 7

S5VLO 2 2

S6NAME F F

S6VHI 2 2

S6VLO 1.3 1.45

S7NAME F F

S7VHI 1.4 1.55

S7VLO .8 .8

**** 05/26/15 16:00:43 ********* PSpice 9.2 (Mar 2000) ******** ID# 1 ********

** Profile: "SCHEMATIC1-000" [ D:\LTD\ep-schematic1-000.sim ]

**** Digital Gate MODEL PARAMETERS

******************************************************************************

D_PLD_GATE D_ACT05

TPLHMN 0 2.800000E-09

TPLHTY 0 6.300000E-09

TPLHMX 0 9.800000E-09

TPHLMN 0 2.400000E-09

TPHLTY 0 5.450000E-09

TPHLMX 0 8.500000E-09

**** 05/26/15 16:00:43 ********* PSpice 9.2 (Mar 2000) ******** ID# 1 ********

** Profile: "SCHEMATIC1-000" [ D:\LTD\ep-schematic1-000.sim ]

**** Digital IO MODEL PARAMETERS

******************************************************************************

IO_PLD IO_ACT_OC IO_DFT IO_ACT

INLD 5.000000E-12 5.000000E-12

DRVL 18.7 18.7

DRVH 1.000000E+06 24.5

AtoD1 AtoD_ACT AtoD_STD AtoD_ACT

AtoD2 AtoD_ACT_NX AtoD_STD_NX AtoD_ACT_NX

AtoD3 AtoD_ACT AtoD_STD AtoD_ACT

AtoD4 AtoD_ACT_NX AtoD_STD_NX AtoD_ACT_NX

DtoA1 DtoA_AC_OC DtoA_STD DtoA_AC

DtoA2 DtoA_AC_OC DtoA_STD DtoA_AC

DtoA3 DtoA_AC_OC DtoA_STD DtoA_AC

DtoA4 DtoA_AC_OC DtoA_STD DtoA_AC

TSWHL1 490.000000E-12 477.000000E-12

TSWHL2 490.000000E-12 477.000000E-12

TSWHL3 490.000000E-12 477.000000E-12

TSWHL4 490.000000E-12 477.000000E-12

TSWLH1 3.619000E-09 470.000000E-12

TSWLH2 3.619000E-09 470.000000E-12

TSWLH3 3.619000E-09 470.000000E-12

TSWLH4 3.619000E-09 470.000000E-12

TPWRT 100.000000E+03 100.000000E+03 100.000000E+03 100.000000E+03

IO_AC_DTOA

TPWRT 100.000000E+03

ERROR -- Convergence problem in transient bias point calculation

Last node voltages tried were:

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( IN1) 0.0000 ( IN2) 0.0000 ( OUT1) .0390 ( OUT2) 265.9E-09

(N00527) 1.9764 (N00654) 2.8228 (N00719) 1.1284 (N00907) 2.3924

(N01006) 1.1284 (N17924) .2820 (N19423) 1.9764 (N19546) .0565

(N19590) .0011 (N19721) 2.8222 (N19887) .0565 (N21991) 1.4114

(N24451) 1.4114 (N74615) -1.4114 (N74771) -1.4114 (N74804) -.7057

(N74983) -2.8228 (N78641) 1.4113 (N78662) 1.4113 (N89744) -.8202

($G_DGND) 0.0000 ($G_DPWR) 2.8228

(X$N78641_DtoA1.DGND_OL) 104.2E-06 (X$N78662_DtoA1.DGND_OL) 104.2E-06

DGTL NODE : STATE DGTL NODE : STATE DGTL NODE : STATE DGTL NODE : STATE

(N00527$DtoA) : 1 (N00719$AtoD) : X (OUT1$AtoD) : 0 (IN2$AtoD) : 0

(N19423$DtoA) : 1 (OUT2$AtoD) : 0 ( N00465) : 1 (N78641$DtoA) : Z

(N19546$AtoD) : 0 (IN1$AtoD) : 0 (N78662$DtoA) : Z ( N19242) : X

These supply currents failed to converge:

I(V_V7) = -10.00GA \ -10.00GA

ERROR -- Discontinuing simulation due to convergence problem

本人是新手,很多问题不知道如何解决 在此请求各位大侠相助

哇撒,大神啊,我看都看不懂!

我只能说,我服了!

是新手 给大家添麻烦了 图中是pspice的原理图 以及仿真结果 但无法仿真 不知道 所在