差分对约束有些乱了 不是配对信号 怎么回事?

时间:10-02

整理:3721RD

点击:

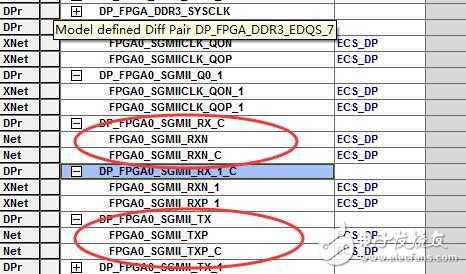

我PCB已经分配了器件模型 但是由于布线不好走进行了原理图信号调整 再从网络表导入进来 发现我原来设置的差分对约束有些乱了 不是配对信号 怎么回事?

包地线确实是会影响到阻抗,但是你自己可以算一下,计算包地线的线宽和间距一直在变化,阻抗的变化也不太大,也就3欧姆左右,个人认为没有关系,还没有加工带来的误差大主要是地孔的距离才是关键,距离不能保证建议不抱地

主要是地孔的距离才是关键,距离不能保证建议不抱地

你觉得呢,你可以把地线当作普通的信号线去看,窜扰形成的原因是什么,嘿嘿

地孔带来的电感效应会更大一些,地孔带来的电感效应会更大一些

地孔 的间距满足入/20,保底没有底孔或者间距很大,没有什么用,遭殃会有噪声的,嘿嘿

对 ,少了 电感效应就上来了