求大神解惑

时间:10-02

整理:3721RD

点击:

单片机的乘法指令和除法指令怎么运算的?求详细过程

硬件乘法器的实现本质是“移位相加”。对于二进制,乘数和被乘数的每一位非0即1,相当于乘数中的每一位分别和被乘数的每一个体位进行与运算,并产生其相应的乘积位。这些局部乘积左移一位与上次的和相加。即从乘数的最低位开始,若其为1,则被乘数左移一位并与上一次的和相加;若为0,左移后以全零相加,如此循环至乘数的最高位。

8位移位相加型硬件乘法器应包括16位锁存器、8位移位寄存器、8位乘法器、8位加法器等4个组成部分。具体电路结构可以自己搜一下。

锁存器发挥着锁存的作用,用于锁存部分和。

移位寄存器则具备移位作用,当加载信号有效时乘数将加载于8位右位寄存器,随着时钟上升沿的到来,乘数即由低位开始逐位移出。

乘法器功能类似一个特殊的与门。有两个输入端口,一个端口用于输入8位并行操作数(被乘数),另一个端口在时钟信号控制下输入由移位寄存逐步移出的串行操作数,并将这两个操作数进行与运算。

加法器用于将本次时钟脉冲控制下得到的8位部分积与锁存于锁存器高8位的前一个时钟脉冲下得到的部分和相加。 你可以研究下参考下51的指令集和特殊功能寄存器。

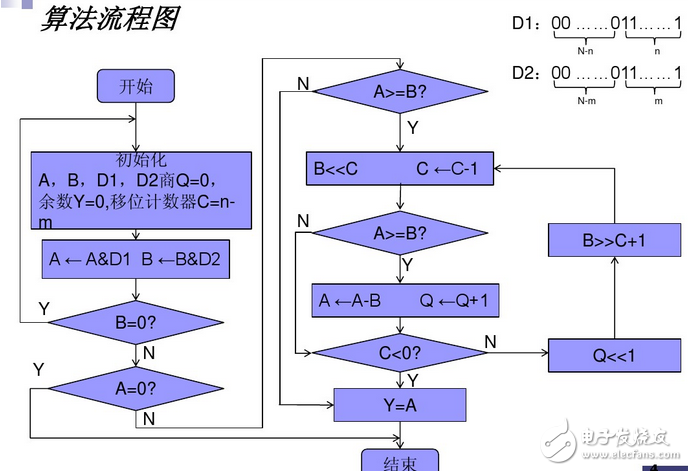

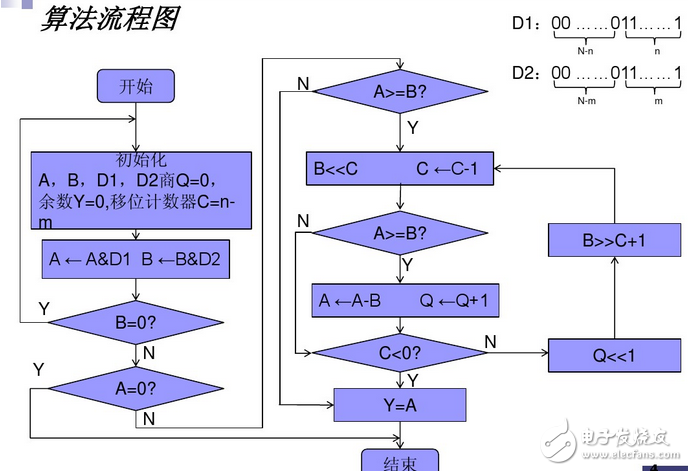

除法类似乘法,也是处理二进制除法,比如有一种除法器,

这个你要看不懂,给你来个形象的,啥是除法?就是A里能找出几个B,你想象A是一个比较长的圆柱体,B是一个短的圆柱体,A和B底面积相同,问你A里面有几个B,计算机的算法就是A和B对齐一头开始比,有一个商计数器加1,然后比划着B的尾端在A上画个道,B往后移头对齐那个道,如果B的尾端没超过A的尾端,再画个道,商加1。直到B的尾端超过了A的尾端,最后剩下那段A是余数就是模,商计数器是多少就是A除以B的整数部分,这就是循环减法算除法,充分发挥计算机喜欢循环做某种简单操作的特长

你的意思是用汇编怎么解决的吗?

我曾经用汇编做过,最大支持16位的数据乘除,方法用的查表的办法,个人感觉比编译器反汇编的算法要快

我刚学单片机,老师说的我听不太懂

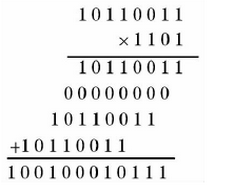

说乘法,分析一下两个二进制数相乘的过程:

硬件乘法器的实现本质是“移位相加”。对于二进制,乘数和被乘数的每一位非0即1,相当于乘数中的每一位分别和被乘数的每一个体位进行与运算,并产生其相应的乘积位。这些局部乘积左移一位与上次的和相加。即从乘数的最低位开始,若其为1,则被乘数左移一位并与上一次的和相加;若为0,左移后以全零相加,如此循环至乘数的最高位。

8位移位相加型硬件乘法器应包括16位锁存器、8位移位寄存器、8位乘法器、8位加法器等4个组成部分。具体电路结构可以自己搜一下。

锁存器发挥着锁存的作用,用于锁存部分和。

移位寄存器则具备移位作用,当加载信号有效时乘数将加载于8位右位寄存器,随着时钟上升沿的到来,乘数即由低位开始逐位移出。

乘法器功能类似一个特殊的与门。有两个输入端口,一个端口用于输入8位并行操作数(被乘数),另一个端口在时钟信号控制下输入由移位寄存逐步移出的串行操作数,并将这两个操作数进行与运算。

加法器用于将本次时钟脉冲控制下得到的8位部分积与锁存于锁存器高8位的前一个时钟脉冲下得到的部分和相加。 你可以研究下参考下51的指令集和特殊功能寄存器。

除法类似乘法,也是处理二进制除法,比如有一种除法器,

这个你要看不懂,给你来个形象的,啥是除法?就是A里能找出几个B,你想象A是一个比较长的圆柱体,B是一个短的圆柱体,A和B底面积相同,问你A里面有几个B,计算机的算法就是A和B对齐一头开始比,有一个商计数器加1,然后比划着B的尾端在A上画个道,B往后移头对齐那个道,如果B的尾端没超过A的尾端,再画个道,商加1。直到B的尾端超过了A的尾端,最后剩下那段A是余数就是模,商计数器是多少就是A除以B的整数部分,这就是循环减法算除法,充分发挥计算机喜欢循环做某种简单操作的特长

翻书去吧!

谢谢