Why output voltage so small?

时间:04-05

整理:3721RD

点击:

Hi,

I am simulating RF self-biased cascode power amplifer in Cadence under the paper below:

A 2.4GHz, 0.18μm CMOS self-biased cascode power amplifier. (attached below)

My problem is that the output voltage, Vout, is even smaller than input voltage, Vin. Meaning that it doesn't amply at all even attenuate input signal.

Could anyone help?

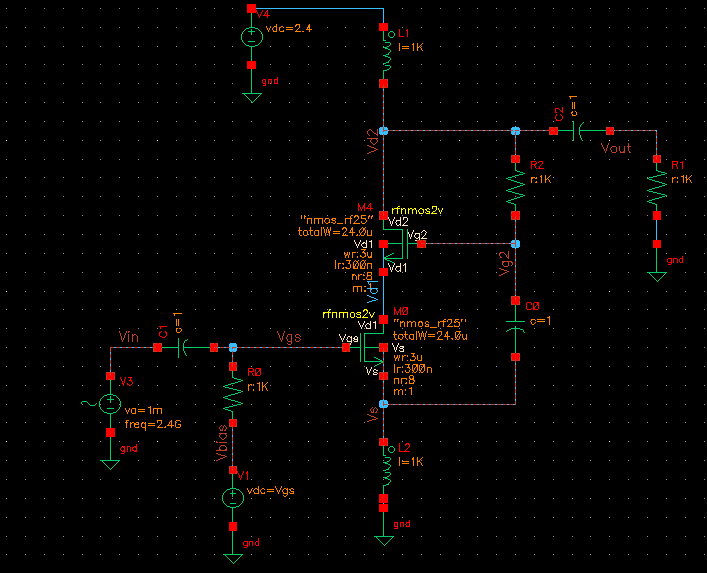

Here is the simulation schematic:

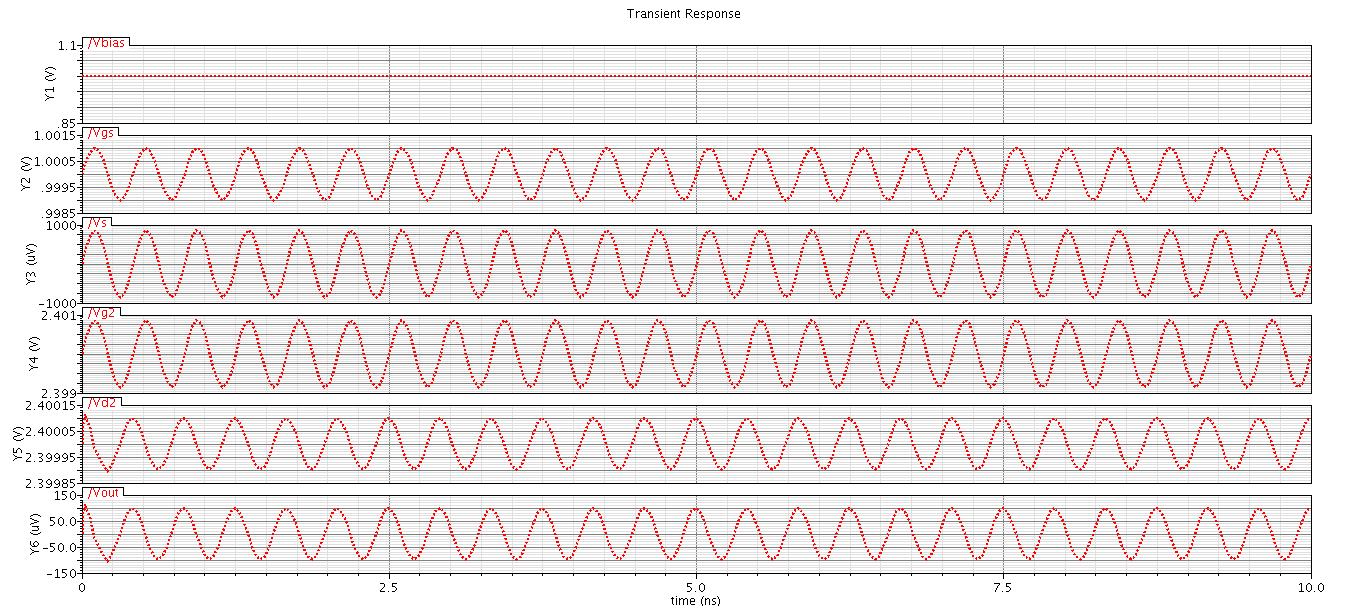

And this is waveforms at some important nodes:

And the paper:

I am simulating RF self-biased cascode power amplifer in Cadence under the paper below:

A 2.4GHz, 0.18μm CMOS self-biased cascode power amplifier. (attached below)

My problem is that the output voltage, Vout, is even smaller than input voltage, Vin. Meaning that it doesn't amply at all even attenuate input signal.

Could anyone help?

Here is the simulation schematic:

And this is waveforms at some important nodes:

And the paper:

Why the 1KH inductor in the source you don't RF choke the ground. This is what kills your gain (A~=Zo/Zs). What you did is a MEGA source degeneration. remove L2 with a short and try again.

Good luck !

Its a SIMULATOR, fiddle about with component values, add extra Cs and Ls and see how they alter the parameters . That how you learn.

Frank

- Induced voltages on transmission line by plane wave in HFSS

- Klystron output voltage, cavity field strength

- Negative voltage needed in K-band

- How to set the bias voltage of the BJT in Gilbert mixer

- is DC voltage gain not an important issue to consider in LNA designing?

- Power (Voltage / Current) inducted in rectangle antenna.