How to plot Cgs Vs Vgs in ADS

Can you tell, how to plot Cgs Vs Vgs in ADS.

Thanks

Kadi

https://www.edaboard.com/thread165432.html#2

Hi.., that you mentioned about frequency dependent capacitance .. But i need Bias dependent capacitance, (How to plot Cgs vs Vgs ).

"Rather I use AC analysis with AC_Vgs=1 and swept DC_Vgs.

Here Cg is evaluated by AC_Ig/(j*2*pi*freq)."

Than that i can find the capacitance from the location of "./kadi/filename/spectre/schematic/psf/dcOpinfo" folder from cadence. But that too single capacitance value... with that how can i can plot .....?

I am new to this tool, Can you explain more ...!

Thanks

kadi

[b]

Calculated Capacitance's dependencies are two varilables, Vgs and freq.

So Cgs=Cgs(Vgs, freq).

So If you do single frequency point AC Analysis, dependency of Cgs is only Vgs.

Surely read my append.

https://www.edaboard.com/thread165432.html#2

What do you mean by cadence ?

There is no tool whose name is cadence.

Use correct terminology.

Show me the followings with the correct terminology.

(1) Design Framework you use.

e.g. Keysight ADS, Cadence dfII, etc.

(2) Simulator you use.

e.g. Keysight ADSsim, Keysight GoldenGate, Synopsys HSPICE, Cadence Spectre, etc.

(3) Post Processing Environment you use.

e.g. Keysight ADS, Synopsys CosmosScope, Synopsys CustomWaveView, MathWorks MATLAB, Cadence ADE(Wavescan or ViVA).

I can not understand what you want to mean at all.

What is "this tool" ?

I can not know what tool you refer at all.

If you use DC OP Analysis of Cadence Spectre and Cadence ADE as Post Processing,

see http://www.eecs.tufts.edu/~ryun01/gmid_ruida.pdf

Before posting, surely learn correct terminology.

This thread is regarding ADS.

The following is for AC Analysis with swept DC_Vgs using

Keysight ADSsim as Simulator

and Keysight ADS as Post Processing Environment.

https://www.edaboard.com/thread165432.html#2

The following is for AC Analysis with swept DC_Vgs using

Cadence Spectre as Simulator

and Cadence ADE as Post Processing Environment.

http://www.designers-guide.org/Forum...1283600359/1#1

http://www.designers-guide.org/Forum...1196459940/1#1

Even if you use Keysight ADSsim as Simulator, you can use Cadence ADE or Synopsys CustomWaveView as Post Processing Environment.

Even if you use Cadence Spectre as Simulator, you can use MathWorks MATLAB or Synopsys CustomWaveView as Post Processing Environment.

Before posting, surely learn correct terminology.

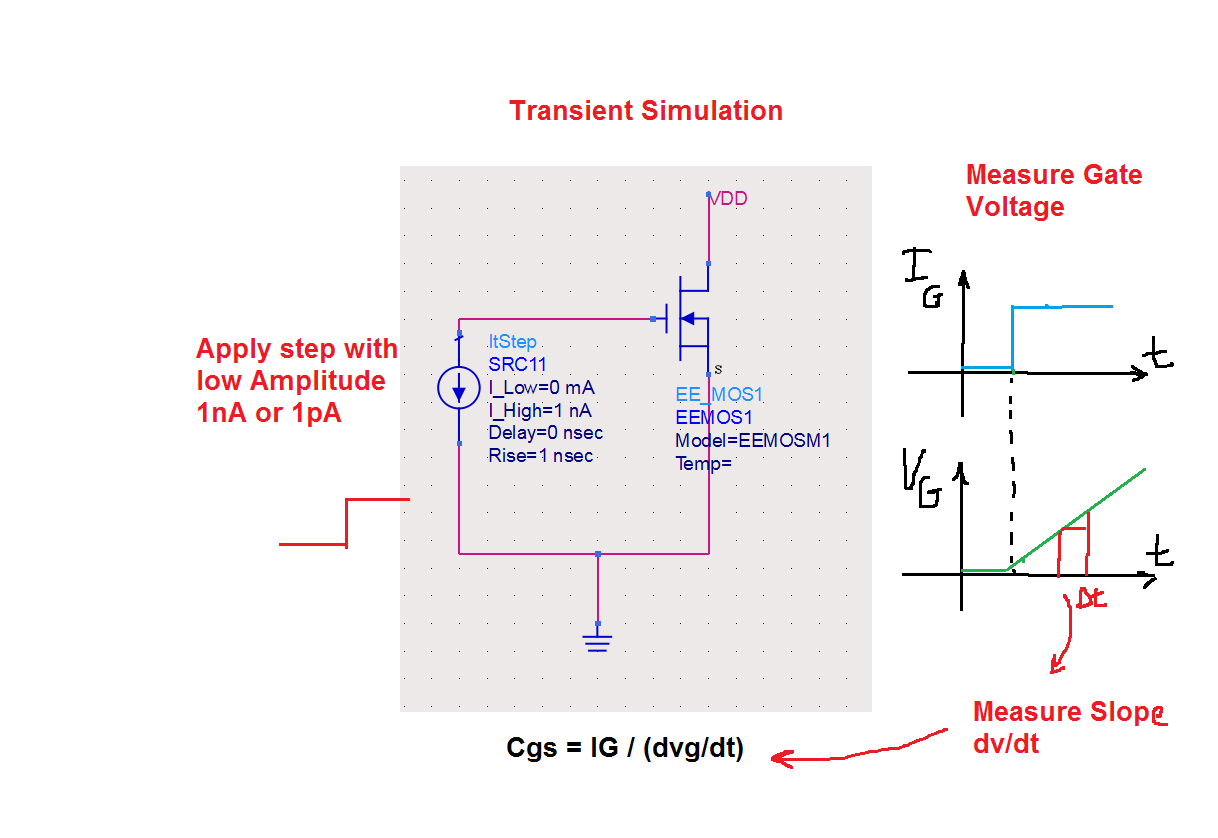

Follow my instructions in this image. Good luck.

Driving gate-source by current is not appropriate.

If gate-source is drived by current, gate is floating.

Here simulator attaches Gmin=1e-12 to gate-gnd to determine DC operation point.

When we use Transient Analysis for evaluation of Cgs, drive Vgs as ramp wave voltage and then capture Igate.

Cgs=Igate/alpha, where alpha=dVgs/dt=constant.

Ramp wave voltage driving is used in actual measurement using actual instruments.

Here actual measurement does not mean EDA Tool Play.

I see this simulation many times. I did this many times for our chip design and I am quite sure that it is correct. I tested it and compared it with other results. It quite simple, since we have capacitance load at input, why not applying a step current to a capacitor and see voltage variations. I even extracted the Mos capacitor curves with this method and drew Cg vs Vgs curves which was persice too,

I was observing the frequency change of VCO with tuning Varactor and I calculated the values which were equal to results I got from this simulation.

Gate is floating.

Gate bias can not be determined without virtual Gmin=1e-12.

Learn actual measurement.

In actual measurement, Cgs is mesured by followings.

(1) By measureing S11 using Vector Network Analyzer.

This corresponds to SP or AC Analysis with sweeping Vgs.

(2) By measuring Igate with ramp wave Vgs drive.

This corresponds to Transient Analysis.

However it is difficult to estimate valid frequency range of Cgs.

Why it is floating ? It has a voltage and it is increasing. In low voltages we are in depletion and cgs will be lower and in high voltage accumulation occurs and we will have maximum cgs. I measured this and values are correct.

He is talking about ADS and plot, you say measure with VNA? I do not get it. I am talking about simulation not real world.

You can not understand Simulator at all.

There is no DC path to gate if you use current source.

So simulator attaches Gmin=1e-12 to help DC convergence.

Surely see logfile of simulator.

And step pulse current drive is not realstic, even if DC voltage can be determined.

EDA Tool Play is no more than Play.

Simulator should be emulation of real world.

And it is very suspicious that he is talking about ADS and plot.

I hear too much gratuitous arbitrary statements in this thread...

Although the gate is floating in the post #5 schematic with current source, the transient analysis can well work by setting an initial condition for Vgs or skipping initial solution.

It is correct if initial condition is set.

However I don't think skipping initial solution is possible.

Floating node treatment is different between various simulators.

See http://www.designers-guide.org/Forum...num=1227157914

I don't mind what method Ata_sa16 use at all.

However ramp wave Vgs driving is common and realistic method than step pulse current drive.

There is no problem in driving drain or source by current.

However driving gate by current is not realistic.

This method was used for MOS Model Level-1, Level-2 and Level-3 which have not good AC model.

However current MOS Models have good AC model, so we use AC Analysis not Transient Analysis for evaluation of Capacitor in MOS.

I am also not doing this simulation by myslef. I am a PHD student and I am experienced. This method has been suggested by my supervisor. He is a full professor and I think if it was wrong he would have mentioned to me.

You already agreed that it's possible to drive the gate with a current source if necessary prerequisites are met.

I don't believe that "realistic" is a useful category for dedicated simulation circuits. There's in fact a large number of simulation setups that are nor realistic in terms of regular circuit design, but useful to determine specific component or circuit parameters, e.g. unrealistically large component values, all kinds of ideal components.

Furthermore, there are real MOSFET circuits with a (in a first order) current driven gate, supplemented by a means that sets the DC bias.

But driving the gate by a current step or a voltage ramp are only different ways to stimulate the simulation, in both cases the voltage dependent capacitance will be determined by the same equation Cgs(Vgs) = dQg/dVgs.

If Cgs is only weakly frequency dependent, the measurement in transient analysis will give almost the same result that a parametric small signal AC measurement with Vgs variation.

No.

If MOSFET is controled from gate, it is a voltage controled device.

BJT is a current controled device.

What do you mean by "first order" ?

There is a problem in an initial behavior for current step stimulus.

On the other hand, there is no problem for voltage ramp stimulus.

MOS Model Levle-1,2,3 give fairly different results between AC and Transient Analysis.

"First order" means that the source driving the gate has high impedance so that it's current determines the actual Vgs rise and fall time. Can be e.g. modeled by a current source with voltage clamps.

Transistor models say it's controlled by Vbe...

Bias is set by Ib not Vbe.

Sensitivity of Ic for Vbe is very large.

However, even for BJT which is a current controled device, I use voltage ramp stimulus.

What I want to mean is that current stimulus is a realistics for BJT.

However still there is a problem for an initial behavior if we use step current stimulus.

- How do I plot load pull contours using values from ADS plots (P1_Contours) in excel?

- Real time plotting of radiation pattern using matlab

- Can you plot loadpull contour plots from impedance values ?

- Comparison of two antenna polar plots

- How to plot Pout A1 dB compression point versus frequencies

- How to plot Loadline in cadence spectre