[moved] HELP Testbench VGA CORE for AGC 10gbps

时间:04-04

整理:3721RD

点击:

Hello everybody!

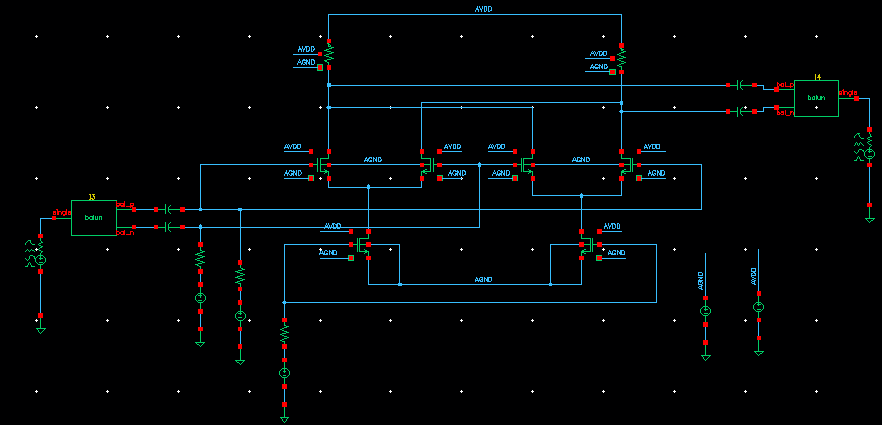

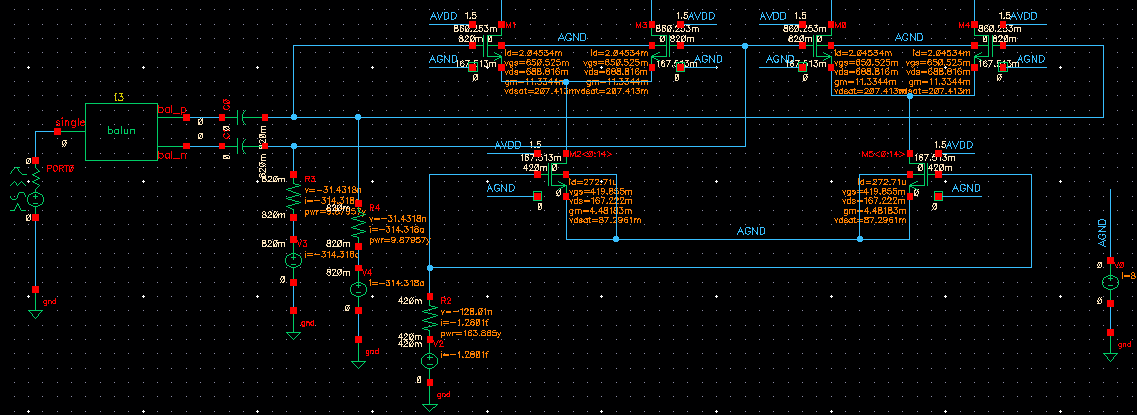

This is my first post, I have 2 years in microelectronics RFIC area. I am trying to design an AGC for optical receiver 10Gbps. I read a lot of papers and I know the blocks necessary to build it now I am in the VGA block but my principal problem is the testbench in cadence.

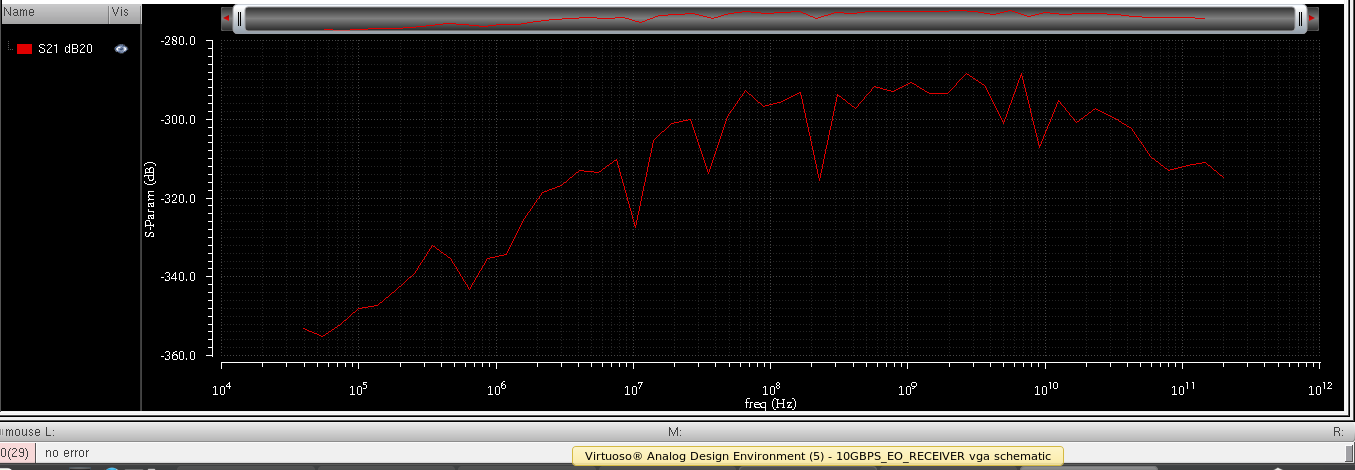

I am trying to measure S21 of VGA, but the result of simulation is very bizarre so I am sure that my problem is in the testbench.

I used this circuit before like FT doubler(Vin+ Vbias Vin-) and it works perfect, now to convert this into VGA I read that the difference is in the connections of the input Vin+ Vin- Vin+, but I have S21 like -300dB.

Please I want to know what I am doing wrong. Thanks a lot!.

Best Regards!

The balun is single ended=50, differential output=100

This is my first post, I have 2 years in microelectronics RFIC area. I am trying to design an AGC for optical receiver 10Gbps. I read a lot of papers and I know the blocks necessary to build it now I am in the VGA block but my principal problem is the testbench in cadence.

I am trying to measure S21 of VGA, but the result of simulation is very bizarre so I am sure that my problem is in the testbench.

I used this circuit before like FT doubler(Vin+ Vbias Vin-) and it works perfect, now to convert this into VGA I read that the difference is in the connections of the input Vin+ Vin- Vin+, but I have S21 like -300dB.

Please I want to know what I am doing wrong. Thanks a lot!.

Best Regards!

The balun is single ended=50, differential output=100

- [moved] Split ring resonator based RFID antenna design in CST ?

- [moved] Fully Cross-Coupled Rectifier Configuration in Terms of Transistor Terminals

- [moved] Intersect errors in Ansoft HFSS

- [Moved]: HFSS API design antenna 5G

- [Moved]: near field to far field transformation code error

- Re: [Moved]: analog filter input/output termination match