KL 系列 FAQ (四)——ADC/DAC 模块

5 ADC/DAC 模块

5.1 KL25 中 AD 模块的 Vrefh 和 Vref l 是什么 ?

问题:

KL25 中 AD 模块的 Vrefh 和 Vrefl 代表什么意思?有何作用?

答案:

VrefH 和 VrefL 是 ADC 的参考电压高电平和参考电压低电平。简单来说,

如果 ADC 的输入信号大于参考电压高电平,则 ADC 输出为满量程;如果输入信

号小于参考电压低电平,则 ADC 输出为零。所以,这两个信号是用来限定输入信

号的测量范围的。

5.2 KL25 中 DADPx,DADMx 两个 AD 差分通道有什么区别?

问题:

KL25 中 DADPx,DADMx 两个差分模拟通道有什么区别,应该怎么用?

答案:

KL25 中的 DADPx 和 DADMx 是差分模拟信号的两个输入端。每一组差分

信号都是用来测量两个信号之间的电压差的。是通过 ADC 进行测量的。差分信号

的输入引脚也可以做为单端的 ADC 输入来使用。有差分通道功能的 ADC 通道,

当你使能了差分功能时,就做差分功能用,如果没有使能差分功能,那就做单端功

能,这个时候和铺铜的单端输入效果是一样的。

5.3 KL15 中 AD 差分输入 问题

问题:

KL15 的 AD 配置为 4 路差分输入,支持交流输入的范围是多少啊?

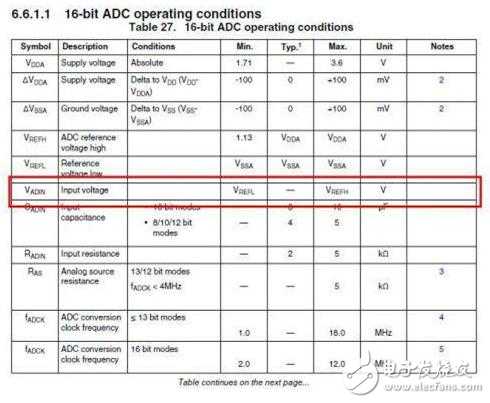

手册里 AD 输入范围为 VREFL~VREFH,可差分输入是+/-REFH 啊?

答案:

差分输入时,差分输入的电压差不能超过 VDDA,每个差分输入端的单端

电压也不能超过 VDDA。

差分采样支持符号位,不过要注意不能接负电压。即单端输入范围只能在 VREFL

和 VREFH 之间。

具体参看下图

5.4 KL02 怎么 没 VDDA、VSSA 引脚

问题:

我用的芯片是 32 引脚的 MKL02Z8VFM4,以前用别的芯片一般都有 VDDA、

VDDS 这种模拟部分用的电源引脚,但怎么我的芯片上找不到?

答案:

有些封装的芯片将 VDDA 与 VDD、VSSA 与 VSS 内部相连了,所以你从芯

片引脚图上找不到 VDDA 引脚。你可以阅读参考手册 KL02P32M48SF0RM 其中

“3.7.1.3 ADC analog su pply and reference connections”章节有提到这一点。哪怕是

同一系列的芯片,不同引脚不同频率的芯片有时也具有差别,这种差别一般都以在

芯片参考手册(Referen ce Manual)的 Chip Configuration 章节看到具体该芯片的配

置。

5.5 ADC 采样 Bandgap 得到的数值不准确?

问题:

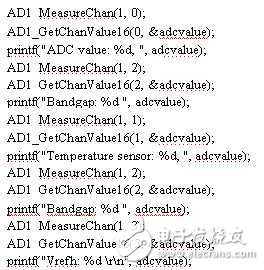

我按照温度传感器测量应用手册 AN3031 操作步骤,打算使用 FRDM-KL25

开发板测量周围温度。用 PE 建立工程,在工程中配置 ADC 的通道 29,27 分别采

样 VFREH 和 Band gap,在代码运行后发现,采样 VFREH 后可转换成稳定的数字

值,但却不能得到稳定的 Bandgap 数字转换值,其偏差程度已远远大于数据手册

标出的±3%准确度。工程代码很简单,其中 ADC 采样部分代码列出如下:

答案:

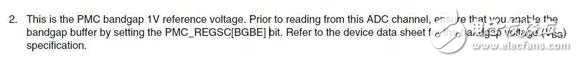

参考 KL25 的参考手册 Chapter 3 Chip Configur ation 说明,配置 ADC 采样 Bandgap

之前,请确保置位 PMC_REGSC[BGBE] 。

参考阅读:

KL 系列 FAQ (三)KL 系列 FAQ (二)

KL 系列 FAQ (一)