求解:关于阻抗匹配后的第三次反射

时间:10-02

整理:3721RD

点击:

我们通常考虑的反射为传输线与输入输出端电阻的匹配。

搭建如下拓扑:

如图所示,传输线阻抗为52.5ohms,将输出端CMOS设置为52.5ohms的输入阻抗,在接收端端接一个10Mohms的电阻接地,相当于开路。

由反射理论可知,源端反射为(50-50)/(50+50)=0,终端反射为

(10000000-50)/(10000000+50)=1。

反弹图如下

应该是没有第三次反射的。

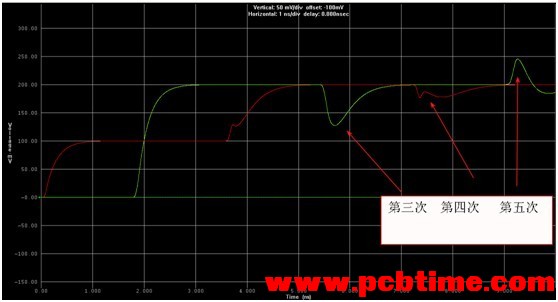

仿真波形如下:

为什么?

我们注意到,在给CMOS赋模的时候,有一个电容值的选项,容值达到了8pf。

在实际上器件是有 C_die 和 C_pkg的, 所以能看到第三次反射。

电容对高速的返回信号成低阻,回来的反射是负反射系数,所以看到是回下来的。

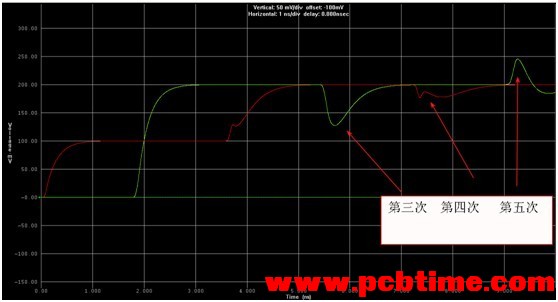

当将电容值改为0的时候,仿真波形如下:

符合反射理论。

电容容值越小,上升沿越抖,越接近设定的上升时间,第三次以及以后的反射也越小。

我们常说的芯片制造工艺让上升沿变抖了所指的就是减小了C_die 和 C_pkg。

搭建如下拓扑:

如图所示,传输线阻抗为52.5ohms,将输出端CMOS设置为52.5ohms的输入阻抗,在接收端端接一个10Mohms的电阻接地,相当于开路。

由反射理论可知,源端反射为(50-50)/(50+50)=0,终端反射为

(10000000-50)/(10000000+50)=1。

反弹图如下

应该是没有第三次反射的。

仿真波形如下:

为什么?

我们注意到,在给CMOS赋模的时候,有一个电容值的选项,容值达到了8pf。

在实际上器件是有 C_die 和 C_pkg的, 所以能看到第三次反射。

电容对高速的返回信号成低阻,回来的反射是负反射系数,所以看到是回下来的。

当将电容值改为0的时候,仿真波形如下:

符合反射理论。

电容容值越小,上升沿越抖,越接近设定的上升时间,第三次以及以后的反射也越小。

我们常说的芯片制造工艺让上升沿变抖了所指的就是减小了C_die 和 C_pkg。