LDO出现的怪现象,求解答

最近一块片子回来发现有这么个问题,工艺是高压工艺,管子VDS为45V,VGS为18V,测出来所有的片子LDO的电源在大约23V以下都工作正常,当超过23V但小于25V的时候LDO的输出就突然变为0了,电流没有特别变化,当继续升高到大约25V以上时候LDO输出突然变为9V以上的高压(设计值是3.3)这时电流比较大了。所有测试情况都是空载。而且当下电之后,再测试还是和之前一样,说明片子也没坏。

最近一块片子回来发现有这么个问题,工艺是高压工艺,管子VDS为45V,VGS为18V,测出来所有的片子LDO的电源在大约23V以下都工作正常,当超过23V但小于25V的时候LDO的输出就突然变为0了,电流没有特别变化,当继续升高到大约25V以上时候LDO输出突然变为9V以上的高压(设计值是3.3)这时电流比较大了。所有测试情况都是空载。而且当下电之后,再测试还是和之前一样,说明片子也没坏。另外电源从0-45V的时候,bandgap全部工作正常。

LDO的montecarlo后仿仿得很彻底了,各种情况都仿真过没问题,另外所有节点的电压也都确认过不会超过工艺限制,那么这是由什么造成的?(PCB和焊接比较糙,但是其他模拟数字功能都正确)

做高压工艺,器件选用一定要小心,有时候仿真是看不出问题的,特别是设计采用低压器件,仿真加高压,有时候还是能通过的。

要在高压走过的所有路径上检查

器件选型 很重要

既然是空载,9V加在分压电阻上会有个增加的电流,LDO超过25V之后增加的电流比起这个电流大很多吗?

觉得有可能是电压超过25V之后,有个器件(或者寄生器件)会从EA往地漏电流,这样环路的增益会大幅下降,加上镜像电流的不匹配,运放的offset变得很大,所以输出到了9V。如果EA是PMOS电流镜,往地漏电流EA功耗不会增加,反之会增大。

可以考虑尝试9V的时候从LDO负载一个小电流,看输出电压是往下直掉,或者还是能保持一定的负载能力,来判断环路是否仍处在反馈状态。

又或者电流源的问题,看来在关键地方加些小的TEST PAD是比较必要的,方便去做FIB

应该是寄生漏电,请问下是否有deep-nwell,p-iso,未接最高最低电平,或者悬浮?

谢谢,确实要注意,不过这个LDO里面都用的是高压器件,并且也检查过各种情况下各个节点的电压都没超过允许值,所以就想不明白了。

谢谢,

既然是空载,9V加在分压电阻上会有个增加的电流,LDO超过25V之后增加的电流比起这个电流大很多吗?

是大了很多,原来是uA,加大变成mA级

觉得有可能是电压超过25V之后,有个器件(或者寄生器件)会从EA往地漏电流,这样环路的增益会大幅下降,加上镜像电流的不匹配,运放的offset变得很大,所以输出到了9V。如果EA是PMOS电流镜,往地漏电流EA功耗不会增加,反之会增大。

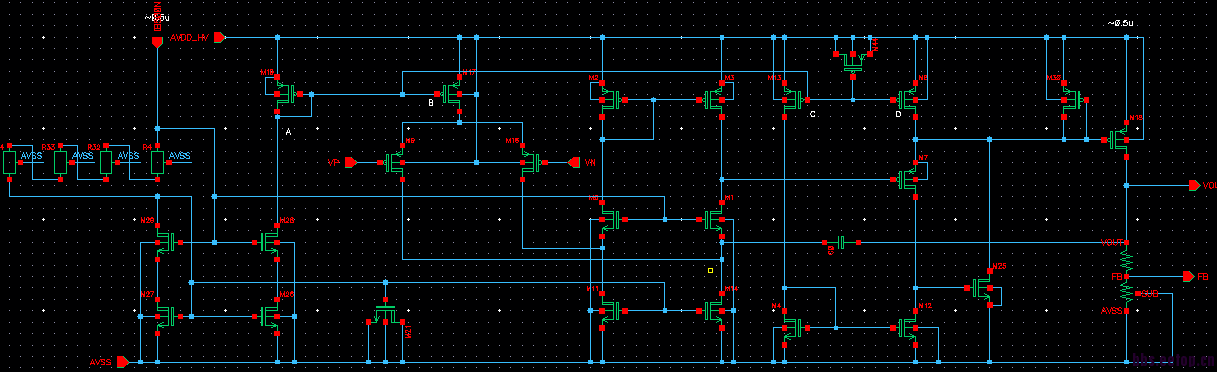

也觉得是这个原因,但是不太理解为何会先掉电后上升,后面关于功耗的变化不太理解,能否详解?我有传电路上去,请看一下

可以考虑尝试9V的时候从LDO负载一个小电流,看输出电压是往下直掉,或者还是能保持一定的负载能力,来判断环路是否仍处在反馈状态。

好主意,试了一下拉几个mA的电流好像没变化,但是电源变化时候LDO输出也跟着变,那估计反馈已经没用了

又或者电流源的问题,看来在关键地方加些小的TEST PAD是比较必要的,方便去做FIB电流

唉,是的

谢谢,还是上图直接,就这两个器件上面是n,下面是p

寄生漏电 也是可能的,看此时总的功耗有什么变化!

漏电电流应该可以仿真的出来

仔细检查版图,保证有源区不能横跨高压金属线,避免高压场开启。

好的谢谢,我检测一下后仿结果的电流

谢谢!提醒我了,DRC这个规则要肉眼检查,当时没检查

25V后这个漏电流本来就受VIN影响,所以VIN变化输出电压也变化

能负载电流,说明环路还是存在一定的反馈,如果内部是完全切换了的话,输出电压就是0V或者VIN了。

想问下EA的输出与VIN之间有加zener来限制PMOS的VGS吗?

还有PMOS输入对管的背栅是接VIN的,当VIN很高时候,能承受20V以上的的背栅-源极电压吗?

想问下EA的输出与VIN之间有加zener来限制PMOS的VGS吗?

没有,没有这个期间,请问用什么器件代替比较好

还有PMOS输入对管的背栅是接VIN的,当VIN很高时候,能承受20V以上的的背栅-源极电压吗?

您说的这个确实是个大问题,不能承受,那么假设BS这个结因为超出限制而反向导通了的话,会发生什么情况呢

想问下EA的输出与VIN之间有加zener来限制PMOS的VGS吗?

没有,没有这个期间,请问用什么器件代替比较好

这个可以用多个diode连接mos串联。

还有PMOS输入对管的背栅是接VIN的,当VIN很高时候,能承受20V以上的的背栅-源极电压吗?

您说的这个确实是个大问题,不能承受,那么假设BS这个结因为超出限制而反向导通了的话,会发生什么情况呢

这个我就无语了,既然BS不能耐高压你不用个pre ldo降压,就敢直接做,你设计电路完全是建立在仿真基础上的啊。没有结合工艺和分析。

说白了,对电路没有思考。光仿真调管子了。

看见人家的一个做法就是功率PMOS和follower的栅极都加一个到VDD的zener,这样可以提供一定保护,让VGS不超过6V

这样的话可以看做PMOS输入管的背栅和源极短接,然后直接和VIN相连,这样这个输入对管就没有PMOS电流镜的电流限制了,因为VREF是固定的电压,VIN输入电压越高,输入对管的VGS和偏置电流变大。

输入PMOS对管进入线性区,漏极电压变得很高,NMOS共栅对管截止,并且源-衬结反向击穿了,形成了从VIN到地的电流通道。

说明工艺不成熟,耐压可能有问题

1)不知道你是不是用的csmc 40v工艺,其中pmos有20v和40v两种,是否误用了20v的。无论如何,有必要向工艺厂再次确认

2)因为bandgap正常,运用对比法排除相同结构的怀疑

3)你不是搞RF的吗?现在怎么客串起高压LDO了?

这个是正解,一般高压管可以承受的Vbs电压要比vds低很多,这个管子的vbs承受电压应该是18V吧,18V+VREF,差不多也就20多点,正好符合你看到的现象,23V以上开始不work,具体有什么behavior最好还是和foundry联系一下,或者问一下process engineer,他们应该更清楚吧

这个可以用多个diode连接mos串联。

既然是要用zener的场合,用mos显然不合适的吧

这个我就无语了,既然BS不能耐高压你不用个pre ldo降压,就敢直接做,你设计电路完全是建立在仿真基础上的啊。没有结合工艺和分析。

这个到不是,本身这个LDO就是用高压管做的,其他模块包括这个模块当初都仔细分析过,只是BS这点不知怎么漏掉了,另外BS结的二极管后仿的时候没有提出来,前仿模型里面也没有,如果有这个模型,仿真也不会没看出来,这个估计是工艺厂的问题了。找到这个diode的类型之后手动加上就能仿出类似错误的情况了。

这个嘛。怎么说呢。

没有zener管的工艺怎么办呢

嗯,太对了,谢谢!

很成熟的工艺,价格也不菲,但确实也有些缺陷,自己设计也有些问题。耐压不够倒是不可能

谢谢!

1)不是csmc

2)说的是,已经在对比看了

3)这个是我们产品的一个模块,别人做的

谢谢,确实是这个问题,我查了这个是heavily doped deep nwell 到p+ diffusion的一个二极管,反向只有7V最高,所以肯定有问题了,但是比较奇怪这个mos里面没有这个二极管的模型,后仿也没提出来,warning都没报,怀疑是工艺厂的问题

你有zener可以用就用,但是你要没有呢?难道去增加成本增加mask。diode的mos放电能力是比zener差,但是方法没问题的。

器件各个结耐压看一眼model就都有了,而且是高压器件,一般都要看的。

学习了

zener不是要靠反向击穿来稳压吗,mos的这个结不击穿相当于没有,击穿的话还能恢复吗