BJT做稳压器,遇到过冲较大的问题(图)

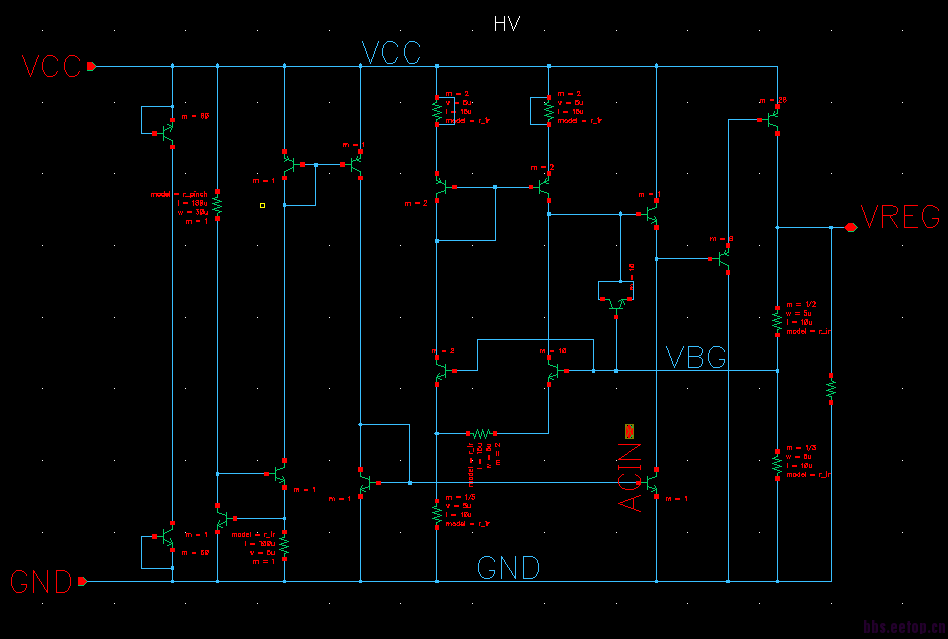

在做一个项目是BJT工艺的,前面的稳压器结构如图所示,这一部分是用的高压工艺做,后面的电路要用低压工艺做。

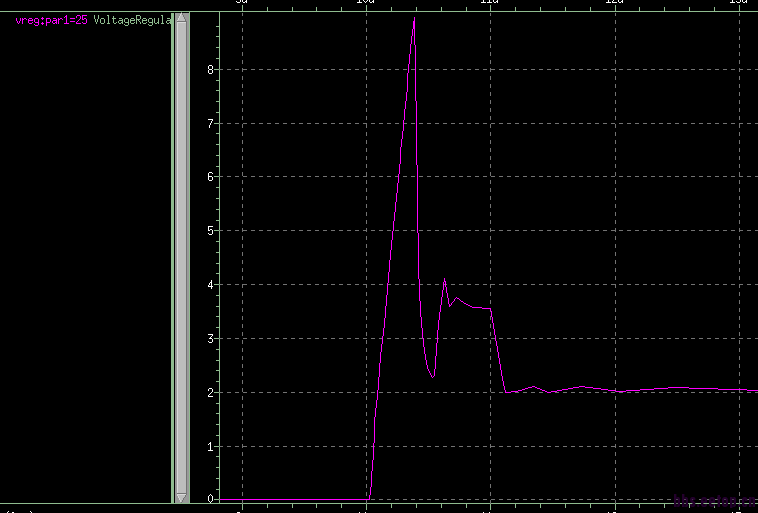

遇到的问题是当供电电压比较大时比如25V,VREG产生的过冲也比较大,这是后面的低压工艺不能承受的。求大神提供解决方法。

你过冲怎么产生的?是负载变化?还是电源?给出图。

图中1应该为横向pnp管,2为纵向pnp管把?。感觉你的环路是正反馈。

请看,输入电压一个阶跃信号,25V,上升时间是1us,VREG的输出瞬间达到了将近9V,这是不行的,虽然我知道这个过冲不可避免,我现在是想办法减小这个过冲

都是横向PNP,整个反馈环路是个负反馈的,里面包括一个正反馈,一个负反馈,但是负反馈要强于正反馈

看到负反馈环路了,VREG加个电容把,你电源上电太快了。你确定下你的应用环境下电源电压上电速度。

真实应用条件可能上电没这么快,因为应用条件的不确定性,所以前仿的时候这里必须通过呀。加负载电容的方法试过了,没有丝毫影响,所以我在怀疑是一些其他的BJT的特性引起的这个现象,比如BJT结电容,基极瞬态电流什么的,您有考虑过吗?

你这个电路给我最大的一个感觉就是太简单了。

bjt电路最主要的就是要看直流工作点,首先在电路工作在稳定状态的时候,频响要好。这个我觉得你是能做到的;其次,电路在Slew和启动的过程中,直流工作点要稳定。bjt由于gm过大的原因使它的线性稳定区域非常小,你这个电路就是在启动的时候有可能有些管子已经工作在饱和区或者截止区。如果有一些管子工作在饱和区或者截止区,那么你的miller电容几乎就不起作用了,频率稳定性也就无从说起了。

你首先要看每个节点的电压电流,找到在启动或者slew过程中有哪些管子的工作状态不正常,然后才能找到方法让这些电路能够正常工作。

之后你要考虑bjt的开关对称性问题,拿你的功率管来举个例子。打开功率管需要基极电流;但是关上功率管呢?如果只是用基极电流的减小、然后靠基极自身的少子逐渐复合关断功率管,那么这个功率管的开关速度就不对称,那过冲就肯定产生了。从这个角度上来说,你起码应该在功率管(PNP)的基极和发射极之间并联一个电阻,以给少子的复合提供外部电流。

总之bjt的电路基本上来说小信号的频率响应设计只在整个芯片设计中占了10~30%左右的工作量,你一定要在各个条件下查看每个管子的直流工作点,然后调整大信号的特性。

多谢指点,我会朝你说的方向去考虑考虑

你最后一pnp管的基极是没有上拉管或者上拉电阻的,这样你想要关闭这个管子的时候就会很慢,就导致你输出电压降下来很慢。但不确定你这个电路结构是经过流片验证没问题的么?结构自己搞的?

还有你最左边的一条支路(串联diode的右边)的电流会随这电源电压正比变化,你电源电压应该到20+了吧?这样那条支路静态电路的变化是不是太大了?

其实你输出可以用NPN,然后输出接个相对较大的电容,overshoot应该比较小!

见过TI类似的一个能自产生reference 电压的HV regulator,外接电容0.1uF,输出管是高压NMOS,输出电压10V,反过来为regulator内部低压电路供电。

一些三端口高压稳压器也是用高压npn做输出的,

或者比起用PNP PMOS管做输出管,用NPN和 NMOS除了dropout电压大的缺点,会有输出电阻小,容易带电容的优点

是的,我也是见到过你提到的电路,我现在这个电路改成另外一种低压差的结构就是抄TI的结构,对于我最开始提到的问题,就是在PNP的基极到VCC串联一个电阻,使基极电流不太快的注入对减小过冲有一定帮助。

我这个应用要做一个低压差的

请教LZ,负反馈路径是怎样的啊?水平太差,没看出来,谢谢

8# thanks

从VBG开始,经过一个有源电流镜,到VREG

确定下你的应用环境下电源电压上电速度