一个SAR的ADC中比较器的失调消除电容问题

时间:10-02

整理:3721RD

点击:

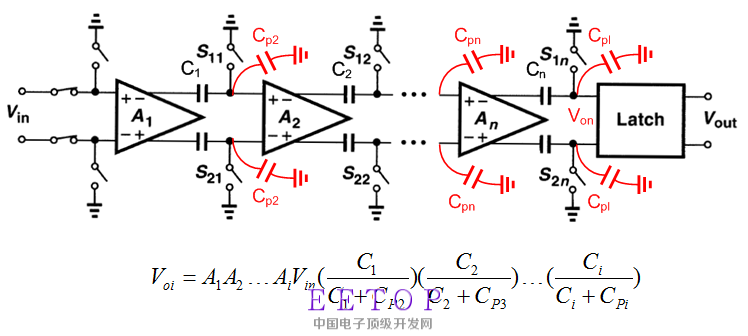

最近在做一个12bit的SAR结构的ADC,其中高速比较器采用的是4级运放加一级latch的结构,四级运放中间每级都有用于失调校准的电容,每级有单独的共模电压偏置。现在没法确定这些电容的值。从目前仿真的情况来看,电容会影响后级运放的输入。不知道这中间有什么诀窍没有。

希望各位大神不吝赐教,谢谢。

希望各位大神不吝赐教,谢谢。

你搜一下IOS和OOS相关的论文,研究下就懂啦

可以推荐两篇么,谢谢

thanks

1.运放输入端寄生电容和失调校准电容一起会分压。

2. 失调校准电容>>寄生电容(10倍以上),否则多个分数相乘会极大的减小输出值。

如果分压比值0.5,那么四级之后,会降为理想值的0.0625倍。

一个SAR的ADC中比较器的失调消除电容问题