单端和差分SAR ADC单位电容选取的区别,有5种不同说法,看看你是哪一种

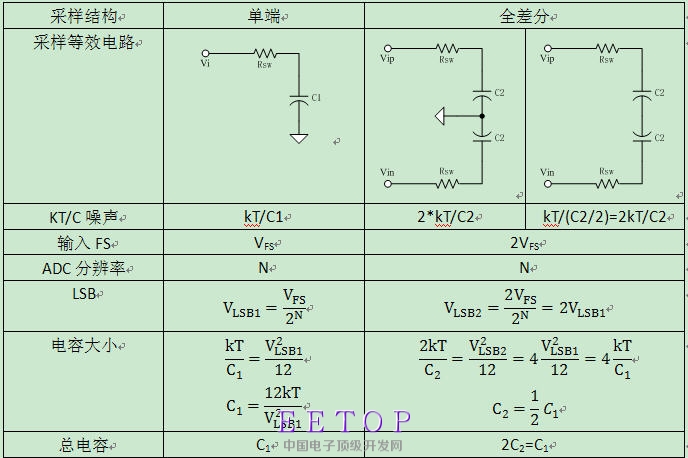

在设计SAR ADC 中最重要的一个问题就是 单位电容Cu的选取。只考虑热噪声的影响,那么问题来了。究竟单端和差分总电容是什么关系?单位电容呢?

因为kT/Cs<(LSB^2)/12,所以Cs>12kT/LSB^2=12kT*2^2N/VFS^2。

那么下面哪一种说法才是对的?

1.差分结构信号摆幅VFS是单端的两倍,所以Cs是单端的1/4,又因为有NP两端,电容加倍,所以差分结构的总电容Cs是单端的1/2;

2.差分结构信号有NP两端,每一端相当于一个单端结构进行采样,和单端结构相等。所以差分结构的总电容Cs是单端的2倍;

3.差分结构信号有NP两端,每一端相当于一个单端结构进行采样,所以相当于Cs=2*C>12kT/LSB^2=12kT*2^2N/VFS^2。又因为

差分结构信号摆幅VFS是单端的两倍,所以差分结构的总电容Cs是单端的1/4。

4.http://bbs.eetop.cn/thread-292719-2-1.html 这是论坛里之前的一个讨论贴

16#

面积变大是指从kT/C的thermal noise角度考虑的?

差分,每个采样电容要2倍,总电容要4C了,那么电容这块面积是增大到4倍了

哦,不过直接用跨接的电容倒只要C

DAC的话应该面积不变吧

5.同上的一个帖子

19#

即使是单端输入也需要双倍的电容阵列.因为, 不用的那一端要用来存储共模电平的电荷.

6.同一贴 23#

无论哪个角度,全差分都不会使电容变大

(1)Noise角度,全差分信号是2倍,信号功率(能量)就是4倍,而全差分的Noise=2*KT/C,所以全差分每个电容的大小可以去1/2C,总的电容还是C

(2)从功能上讲,全差分的MSB的比较不依赖于C的电荷分配,只需要比较全差分信号的极性(大小)即可。也就是说全差分结构的SAR,最高位电容可以省掉。最终全差分的电容总大小和单端仍然一样。

究竟差分Cs是单端Cs的多少倍?差分VFS应该是单端的两倍,但是在Cs计算的公式里怎么体现?

求大神拍,使劲拍,别客气。我自己都想糊涂了……

自己顶一下,这个问题自己琢磨了好久,不知道上面哪一种是对的?希望大家都来说说自己的认识。

得,看来大家觉得这个问题不值一提。但是说法4~6取自已有的讨论帖,说明大家还有分歧,有人认为单端电容1,差分2;有人认为单端差分都是2;有人认为单端差分都是1

我的理解.

感谢你的回复,这是一篇文章吗?可以提供出处吗?

比较激动,还没有仔细看,先赞后看……

再次感谢,自己在这么多种说法里有点糊涂了,所以你这应该是第6种说法,总电容不变,差分结构每一端都只有单端结构的一半;

如果这样的话,差分结构只是在开关功耗上比单端结构差,面积上两者相等。

还有,你是怎么看说法6中

我觉得是不对的,因为差分判断极性本质上和单端与共模电平的比较是一样的,并不能判断接下来开关的打法。SAR ADC的逐次逼近算法本身要求每次都是和一个参考电平Vref的1/(2^i)比较,所以只是简单的极性判断没意义,差分并不能节省电容。

另一方面,有一篇文章Vcm-based开关时序,它也是差分结构。文章里说因为采用Vcm=0.5Vref,所以这种开关时序才省掉了MSB电容。这样不也反过来说明只是差分并不能节省电容?

期待你的回复,主要是没人讨论,自己琢磨太迷茫了……

不是文章, 是自己做的简单对比.

在相同分辨率下, 虽然理论来说差分结构的总电容和单端一样, 但考虑到版图匹配的因素, 差分结构电容阵列面积应该比单端大; 至于差分结构是否可以省掉MSB电容, 没有仔细研究.但从kt/c噪声看, 差分结构的总电容要求和单端一样.

需要这种能算得大牛

厉害了,原来是大神自己推出来的,非常感谢。对于说法5 即使是单端输入也需要双倍的电容阵列.因为, 不用的那一端要用来存储共模电平的电荷.这个也是错的吧?单端需要储存Vcm的电容阵列吗?看到的一些文章Vcm都是直接接在比较器的另一端。

我不是什么大神, 只是很久以前做过sar adc, 大致有些了解, 我见过的单端结构也没有用另一个电容存储vcm.

哈哈,非常感谢你的回复,收获很多……

单端和差分SAR ADC单位电容选取的区别