SAR ADC中MIM电容DAC阵列的画法

觉得你这个后仿结果有点奇怪,一般不可能结果差这么多。请具体说明一下几个问题

1. fully differential or single-ended ADC?

2. 采样速度

3. 工艺

4. MIM cap or MOM cap?

5. 比较器机构。比较器后仿和前方结果对比。

6. 你的DAC版图。这个版图一般就是中心对称来画的。

你好,是全差动结构0.18chrt 工艺,10bit10Ms/s

用的MIM电容,比较器什么的都还没有后仿真,只是单独仿真了电容阵列(即电容阵列是版图,其他还是原理图,主要是为了一个个模块排除)

电容版图没有全对称,主要是有个大牛师兄说过多考虑匹配会带来更多的寄生电容,如果一个个单独摆放效果会更好。

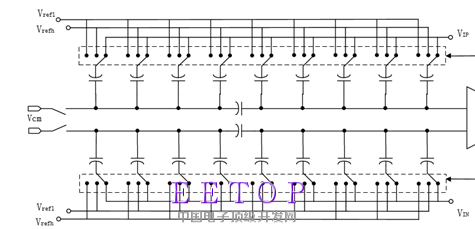

就是这种布局方式,主要是为了让电容引出线更短

要用单位电容来画

是的,我只是画了大概的示意图。请问布线有啥要求。

你用这个工艺能做10Msps,算是比较厉害啊。unit cap放多大啊?

我觉得最好还是用common-centroid方法来做。像你这样的话,会产生比较大的mismatch, 主要是最大的cap 和最小的cap的mismatch.

routing稍微麻烦一下,只会在bottom-plate上产生比较大的寄生电容。对于top-plate, 要保证dacp,dacn两边的寄生电容对称,不会对你的adc产生影响,因为你是differential 结构。

就目前你说的情况看来,最有可能是settling 的问题。检查sampling switch的大小,加上routing的电阻。然后看看最大的cap的bottom-plate switch的大小。

谢谢您的认真回复,恩,我试试对称画法吧。我的最小电容是28f,刚画了数字控制逻辑的版图,单独跑了一下后仿真,数字模块没问题。

但是比较器和电容DAC部分问题都很大。估计主要是我没经验吧。

10M的采样速度确实是我做的极限了,前仿真还可以,不知道版图会不会成功。

您应该在线吧,我给您留了我的联系方式,方便加个好友吗(私信里)

我前一阵子刚画完一个10位SAR ADC的版图,个人心得是其实后方会遇到很多问题,即便你的每个部分单独后仿结果都还OK,最后整体的结果也会有比较大的偏差,电容阵列的话,不知道你有没有分段,我的做法是分段了,分段的话,能省很多面积,你是不是开关跟信号线挨得太近,我最开始就是这样,然后出来的结果比较差,改了之后会有明显效果。比较器一定要尽量对称,对后仿的影响非常大

10 bit ,你最小单位电容28fF, 后仿真8.7bit也不算很差了。

你这个8.7bit有效位数,你有没有FFT的结果,是SNR限制还是THD呢? 个人觉得是你对应的bit位的switch开关管的寄生的影响更大。 因为你还只是后仿真,本身cap 阵列应该mismatch很小, 而对应bit位的switch开关寄生电容可能不是严格2进制match的。

画电容阵列版图时,耦合电容放在低位还是高位?我画出来做后仿的时候逻辑从低位跳到高位就会出错。你觉得是什么原因?谢谢指导!

我不太确定你的问题是什么哎,但是感觉可能是你的比例不对,就是有了寄生之后,实际的低位电容值比实际的高位电容值还要大,这样低位跳高位的时候会出错。我的桥接电容就在高低两段之间呀。

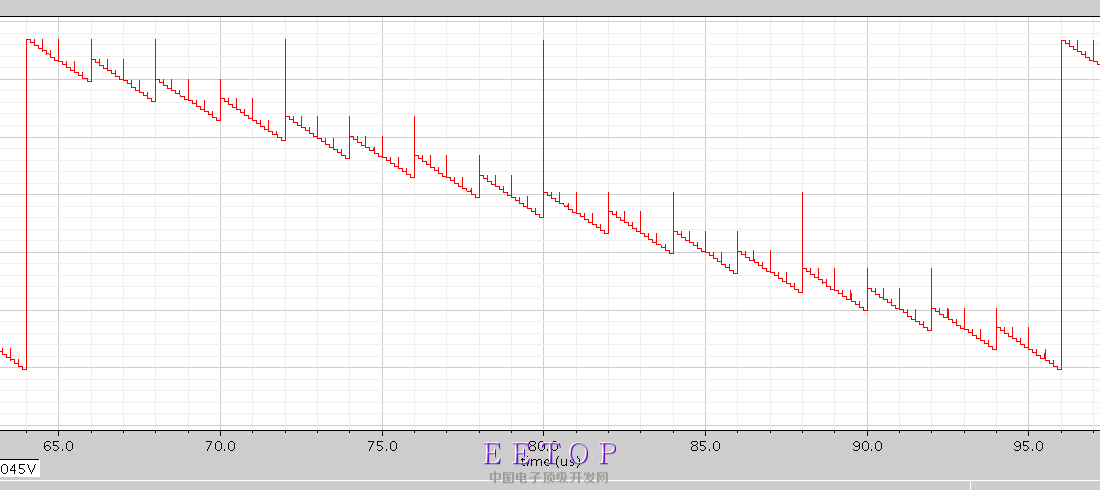

您好!这是我后仿出来的图形。

我说的桥接就是最普通的这种呀,你后仿的时候有没有调整寄生电容的比例?就是说让实际的电容值(理想的+寄生的)成比例?

就是这种结构。我没有调整寄生电容的比例。还请指导怎么操作?画法都是按照共质心结构,dummy电容的画法画的。谢谢!

比如你的电容上极板是m7层,下极版是m6层,那么你就用m6或者m7打补丁,然后看实际电容的大小是否成比例就行啦

请问所说的打补丁具体指什么意思,谢谢。

谢谢分享

learning !

你好,我想问下你说得开关和电容离的太近,为什么会有很大影响啊?我也是这么布局的。

你好,你这里说得调整实际电容值(理论+寄生),我想问下,这里的寄生指的是各个bit位的耦合电容吧,不是指下极板对地的寄生电容吧。请指导。

就是运行calibre之后,RUN PEX,可以看到每一位之间的寄生CC,让CC跟C成相同的比例,这样子寄生的影响就减小了。

对,是各个bit的耦合。

我都有点忘记我之前怎么做的了,不过开关的跳变和信号线耦合,会对信号有干扰。可以的话,保护下信号

受教了,很大的学问啊

SAR ADC中MIM电容DAC阵列的画法