关于SerDes TX RX时钟的问题

我不是高SerDes IC设计的,纯粹是应用层的开发人员。

最近在调试一个基于SerDes的传输协议CPRI,遇到一些问题,还求大家指导!

1. SerDes的RX时钟是CDR恢复的,TX时钟是不是可以来自本地时钟,也可以使用其RX CDR恢复出来的时钟?

2. 我最近在调试CPRI协议,貌似要求的是链路一端的TX时钟必须来自其RX链路的恢复时钟,请问有类似这样的要求吗?为什么?

我理解的是即使CDR恢复了时钟,但是仍然需要协议中插入一下idle码去校准时钟偏差,对于SRIO这种包格式的协议,包与包之间是包含idle码的,所以可以精确恢复时钟。

但是对于类似CPRI这种协议,是流格式的,传输LTE等通信天线数据,由于对时间敏感,不能插入idle码,所以即使CDR恢复了时钟,也是不精确的。其仍然需要将RX恢复时钟经过外部PLL降jitter后在做TX时钟。

大家有没有类似的经验,望知道!谢谢!

PCIE两端是否要求的是REFCLK同源?我看大部分PCIE设计都是一个PLL芯片出来的时钟

tongwen,

1. SerDes的RX时钟是CDR恢复的,TX时钟一般是来自本地时钟,TX在有的特殊情况下会用CDR恢复出的clock,如某些repeater

2.我没做过CPRI协议,简单讲一下我的理解,如果spec要求TX端的clock 来自CDR恢复的clock,可能有一些特殊的要求,比如frequency offset小,SJ趋势一致之类的。

一般来说,这类系统会有这样的问题,就是TX打出去的data会带上CDR恢复出来的clock(也就是RX的DATA)所带来的jitter,有可能是Random jitter,ISI,SJ等。这样另一端的RX能不能正确track这个jitter,信道上的jitter以及会不会有jitter peaking是需要仔细考虑的。

您好!

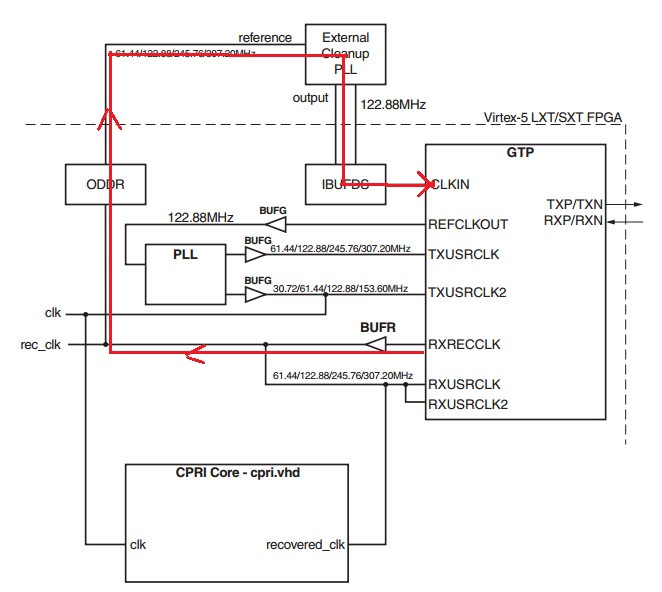

按照我现在理解的,我目前调试的这个CPRI协议,要求,如果两端时钟不同源,则需要在slave一端从RX恢复时钟用作TX,大概如下图所示

这样经过外部的jitter cleaner PLL后不知道还有没有您提及的random jitter、ISI、SJ等一些问题?

根据High-Speed Serial I/O Made Simple的第63页,有这样一句话

“Since we are going board-to-board, we could definitely have different oscillators driving the transmit clock of the transceivers, so we must account for clock correction"

我理解这句话的意思是,如果SerDes链路两端TX不同源,SerDes底层必须要实现clock correction。

这点我不是很理解,因为我感觉SerDes两端TX没必要同源,反正两端都是RX恢复时钟去latch data。

A与B连接,A某个时刻TX时钟为1GHz,B端RX恢复出这个1G去RX;B在这个时刻TX为1.0001GHz,A端RX恢复出这个1.0001GHz去RX。应该没有问题吧?

可是为什么上面这句话提及了TX不同源,则需要进行clock correction,后文提及要在packet之间插入idle序列从而进行clock correction,类似SRIO中的IDLE1、IDLE2。

而CPRI这个协议,是传输时间敏感的无线通信数据等,貌似没有类似的IDLE序列定义

难道是因为CPRI没有这样的IDLE序列,所以在链路两端TX不同源的情况下,无法进行clock correction--------->CPRI要求在链路两端TX不同源的情况下的前提下,一端slave必须用RX恢复时钟去TX

两者能够建立逻辑关系吗?

1.经过外部PLL后,PLL带宽内的jitter还是在,带宽外的jitter会被抑制,打出来的DATA还剩多少jitter就要看具体设计了

2.Serdes系统一般都会规定两端的频偏,因为频偏对CDR的performance影响比较大,尤其是在transition density比较小的时候。有的系统会在spec中直接定义两端频偏的最大值,也有的系统会希望slave端能用master端的clock来用。

因为无线通信中的IQ数字信号数据有着严格的时间性,所以类似以太网数据包的那种传输方式是不适用的,只能通过外部PLL参考RXREFCLK来同步时钟并保持,以尽可能低的方式减少错误的发生。

而以太网数据包或者其他类似的通讯协议没有严格的到达时间,所以可以允许每个数据包单独同步,并用数据缓冲器来消除误差,实现数据的完整传递。另外我个人认为,这类的同步不是使用idle时间完成,而是使用包头的几个字节来完成时间CDR的时间对齐,保证后续有效字节的正确判决。

好东东,学习下

RX CDR恢复的时钟是跟随TX的时钟的,所以TX端采用CDR恢复出来的时钟,主要是最大限度减小频偏,拙见望参考!