请教大家一个ESD问题

I/O怎样对电源端口起保护作

2011-3-19 16:25

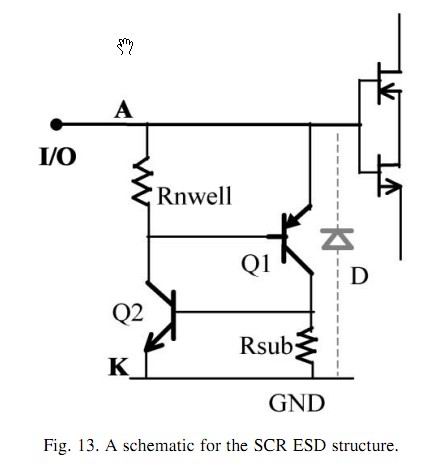

用?IO到VDD之间也可以用SCR啊,可以参考这篇文章

Ming-Dou, K., W. Chung-Yu, and C. Hun-Hsien, Complementary-LVTSCR ESD protection circuit for submicron CMOS VLSI/ULSI. Electron Devices, IEEE Transactions on, 1996. 43(4): p. 588-598.

用是可以用,我也查过相关论文,但是为什麽好多只做一个对地的SCR结构的ESD,难道做一个对地的就够了么?

明道柯ESD

IO到VDD的ESD通路也需要,除非有些电路有特殊要求导致不能在IO到VDD通路加ESD器件,IO相对VDD发生正的ESD脉冲,是正向二极管导通泄放ESD电流,IO相对VDD发生负的ESD脉冲时,就要靠SCR(或者PMOS)来泄放了,或者通过VDD到GND的Power clamp,在通过GND到IO的二极管来泄放电流。

很多文章也许只是强调这个SCR器件的性能,没有强调全芯片的防护。

那不是有个虚线画的二极管么,是不是通过那个二极管来实现负脉冲保护?

学习了

有一些电路会有专门的反接保护电路,这边的ESD一般都是4kV以上的针对MMB,RMB等的瞬时保护

芯片层面侧重“ESD路径”的设计,原则上任何两个pad间只要存在合理的ESD泄放路径即可。某些应用,IO和电源间无直接泄放路径,只存在到地通路,这时候IO如果和电源之间发生ESD事件,电荷会经由地中转,再通过电源和地之间的power clamp泄放

学习一下

我的理解哈,在那些工艺下PMOS的触发越来越不靠谱;

还不如从NMOS走到地再到电源的路径划算;

负向不够了 补二极管

I/O和地,VDD和地之间通常都有专门或者寄生的二极管。I/O, Vdd 接N, 地接P。所以只要I/O 对地有保护,I/O对Vdd也没问题因为电源和地之间就差一个二接管正向导通电压。 Vdd 对I/O 是通过Vdd到地,然后地到I/O。

为什么现在的好多SCR结构的ESD只做对地的保护,这样岂不是负ESD脉冲没办法保护了么?

I/O怎样对电源端口起保护作

2011-3-19 16:25

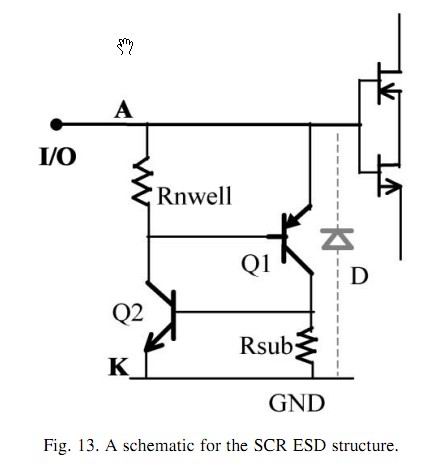

用?IO到VDD之间也可以用SCR啊,可以参考这篇文章

Ming-Dou, K., W. Chung-Yu, and C. Hun-Hsien, Complementary-LVTSCR ESD protection circuit for submicron CMOS VLSI/ULSI. Electron Devices, IEEE Transactions on, 1996. 43(4): p. 588-598.

用是可以用,我也查过相关论文,但是为什麽好多只做一个对地的SCR结构的ESD,难道做一个对地的就够了么?

明道柯ESD

IO到VDD的ESD通路也需要,除非有些电路有特殊要求导致不能在IO到VDD通路加ESD器件,IO相对VDD发生正的ESD脉冲,是正向二极管导通泄放ESD电流,IO相对VDD发生负的ESD脉冲时,就要靠SCR(或者PMOS)来泄放了,或者通过VDD到GND的Power clamp,在通过GND到IO的二极管来泄放电流。

很多文章也许只是强调这个SCR器件的性能,没有强调全芯片的防护。

那不是有个虚线画的二极管么,是不是通过那个二极管来实现负脉冲保护?

学习了

有一些电路会有专门的反接保护电路,这边的ESD一般都是4kV以上的针对MMB,RMB等的瞬时保护

芯片层面侧重“ESD路径”的设计,原则上任何两个pad间只要存在合理的ESD泄放路径即可。某些应用,IO和电源间无直接泄放路径,只存在到地通路,这时候IO如果和电源之间发生ESD事件,电荷会经由地中转,再通过电源和地之间的power clamp泄放