带斩波运放带隙基准的诡异偏置点

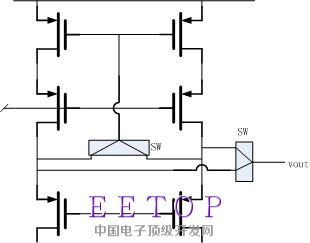

上述带斩波运放带隙基准TRAN仿真时偏置点一直不对,正常为右图,实际为左图,即运放有一边不导通(输入对管为PMOS)。(正负反馈解法正确)请问

1:这种结构不是只有正常状态和零电流两个简并点么?我仿出来的这种是怎么回事?我计算了正负反馈系数为-0.78和-0.42,没问题啊。

2:基于诡异情况,难道自启动电路需要在3个点注入电流么?运放正负输入端和输出端?

谢谢!

自己顶一下,希望哪位回复下。谢谢!

误差放大器里面呢?

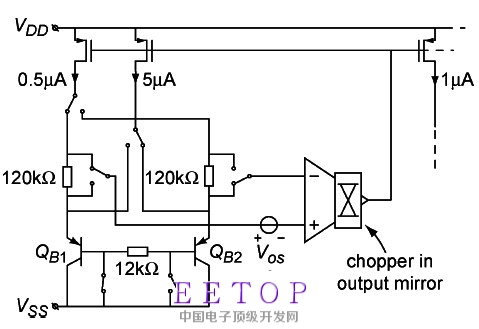

运放输出一个写成了558m,实际也是550m

1.右边的运放输出为1.75V, 左边的为0.55V,是否此时的输出N管已经进入线性区了,导致放大倍数不够。

我来说下,首先,要chopping前后要保证bandgap的接法不变,也就是负反馈大于正反馈,运放的输出接法应该是这样的

其次,如果没有启动电路,这个电路会有启动问题。用bandgap的电流来为opa提供电流,更要注意。

谢谢,

斩波运放的输出端是按照您给的图示接的。

启动电路不是只能解决0偏置电流的问题么?这种非零偏置电流,但是却不对称的状态,自启动电路能解决吗?

运放有一边不导通是什么意思?

运放的两个输入切换图上看不清楚;运放的输出切换有没有弄错,也就是说输出切换后,运放作为黑盒子,输入端正负是不是还是遵循右图?

另外,主极点补偿有没有问题?

chop频率是多少?从图中看不出这些信息;

找到原因啦;

查找方法:将斩波时钟固定(一个为2.8,一个为0),然后在运放输出点断开扫直流,发现有3个简并点。将该状态与没有时钟正常状态比较,发现是由于基极电流太大,导致最下面的两个NMOS开关有大电流通过,从而使得A点电压为500m,而不是正常状态的0V。

解决方法,将最下面的两个NMOS开关尺寸加大

遗留问题:即使尺寸很大,因为有电流通过,所以A点不可能完全为0,唉,大家怎么解决的啊?

没在bip这里用过NMOS开关,请问这里的开关的作用是什么?如果电流过大,通常采用在通路中串个适当的电阻限流,比如在pmos电流镜的drain串个几十上百k电阻。

结合斩波CLK使用,由于设计中左右两边对称的,所以需要开关来通断左右三极管,这样可以消除三极管的失配。具体可以参见下图

lz这个是用来做温度传感器的吧,我也遇到过,是简并点的问题