class D的几个问题求助

在class D的输入端需要加buffer吗?如果加的话buffer的噪声岂不是直接被后级的class D放大?系统的噪声就很难被压到最小。

尽量降低buffer的噪声,应该不难做。

请问你整体SNR的需求是多少呢?

谢谢你的回复!

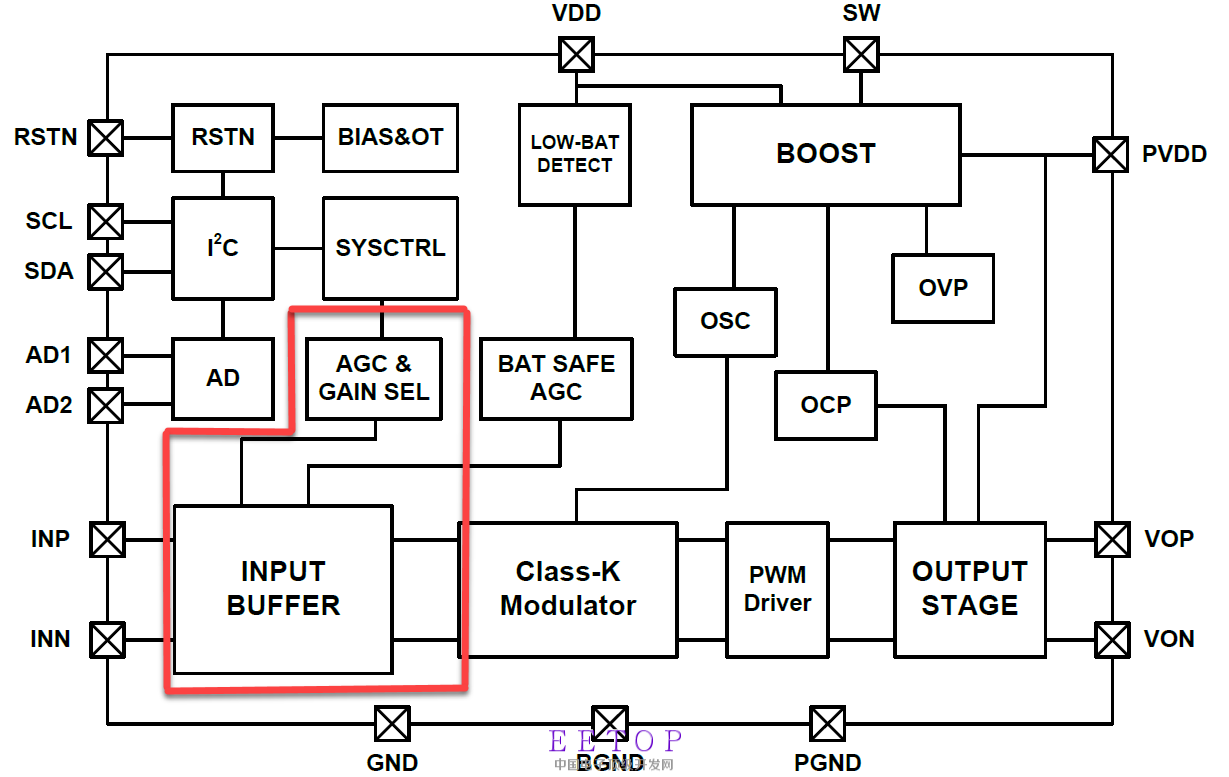

由于class D的输出功率管是8.5V boost converter供电,电源的供电电压为2.5V~5V,在供电电源为2.5V的情况下class D至少需要分配8.5/2.5=3.4倍的增益,考虑到信号的裕量,大概class D需要分配4倍的增益。从噪声方面考虑的话,AGC增益的调整就只能放在输入buffer上,同时输入的buffer需要与外部的高通滤波器的电容(47nF)配合,buffer的输入电阻在10K左右(保证不滤除音频信号)。假设输入buffer的输入电阻和反馈电阻都为10K,然后class D的输入电阻为25k,反馈电阻为100K,我用理想的运放模型,只是计算电阻的热噪声,在音频范围内(20~20KHz)的积分噪声也超过了23uV,现在看到MAX,NXP,TI有的产品在4倍增益的情况下噪声都低于20uV,所以有些疑问,这个buffer到底是否需要?

了解,只要classD稳定度都够,其实PGA不见得需要

好的,谢谢你的回复!

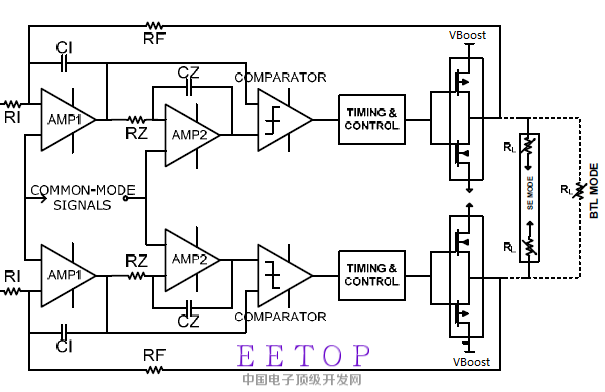

还有一个问题就是classD的输出功率管的供电时8.5v,调制器的供电电压为2.5~5V,采用下图电路结构会造成输入与输出的共模电压不一致的问题。就是说在零输入信号的情况下,输出应该是占空比为50%的方波输出的共模为(8.5/2=4.25V),但是由于输入信号的共模电压为vdd/2,这个时候反馈到输入端的电压被钳在vdd/2,这样就会造成输出信号的占空比不是50%,这个问题怎么解决呢?

顶一下!

顶一下!

这个图的paper能share一下吗,谢谢