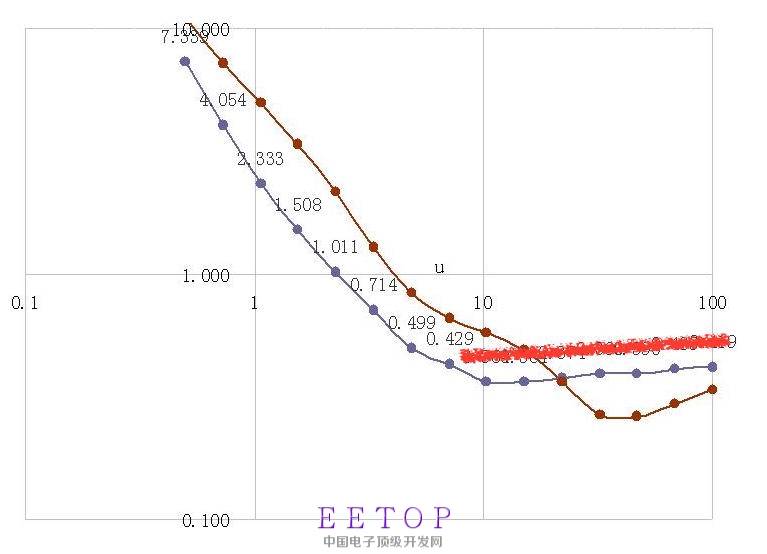

jitter tolerance curve 解释

时间:10-02

整理:3721RD

点击:

神,测出来的jitter tolerance 在带宽小的时候是正常的,在带宽增大时(通过调charge pump 电流)高频会低下去。C1/C2有60倍,所以觉得不是phase margin的稳定性的问题。

求解释,另外有什么文章或者书关于这个理论的。谢谢了.

蓝色是好的,咖啡色Icp是蓝色的4倍。

自举。

hunting jitter 增大?

有带宽小的图吗

贴得几幅图没看出区别

PLL型CDR肯定会有这样的问题,是你的环路阻尼系数太小了。大C大点会好点。

大C很大了,不对呀,Icp小的时候没有问题,Icp增大,阻尼系数增大了,怎么反而有问题了?

增加了好的图。

自举。

顶起来

带宽太大了,而等效参考频率和环路的延时没变。

在带宽大的时候,环路本身的噪声也会变大,所以在高频时对噪声的容忍性就低了。想问一下你这个数据速率是多少,用了哪种振荡器?

所以对于CDR来说,提高jitter tolerance能力并不是带宽越大越好?

看起来像是带宽太高时,带内的jitter吃掉了一部分jitter tolerance, 可以把Icp从4倍变成2倍看看

10G, LC, 那为什么只是在某个频率低下去, 后面又上去了?