关于运放相位裕度问题

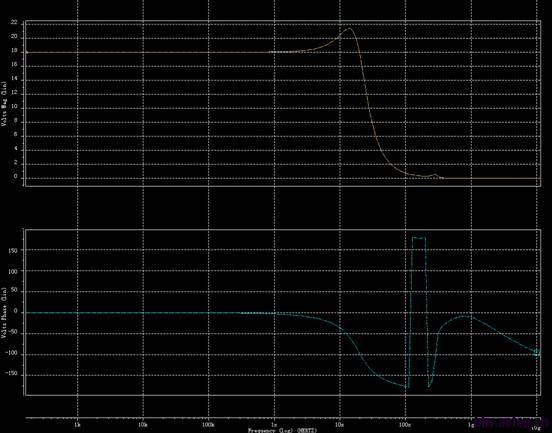

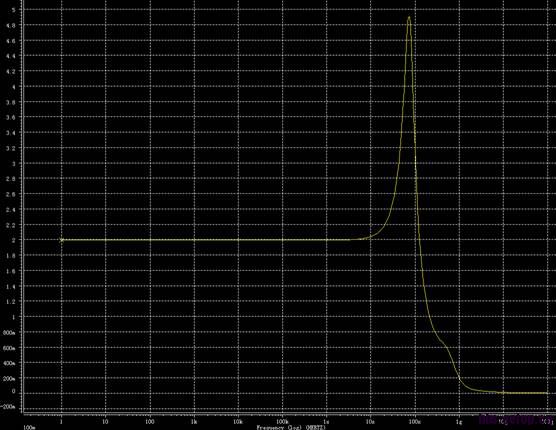

开环测得相位裕度大概有90°,但是闭环情况的增益曲线有个明显阻尼情况,应该是相位为45°时候才应出现的波形

请问大家问题出在哪,我该怎么调整消除阻

自发自回,怎么没有人回答我啊

你的电路开环都有问题,何况闭环..

开环增益高频有个明显上翘,先去掉再说。至于相位,完全看不懂你这相位是怎么弄出来的

check gain margin, and for sure the overshoot at high frequency will cause you instability. That means loop gain transfer function itself is unstable.

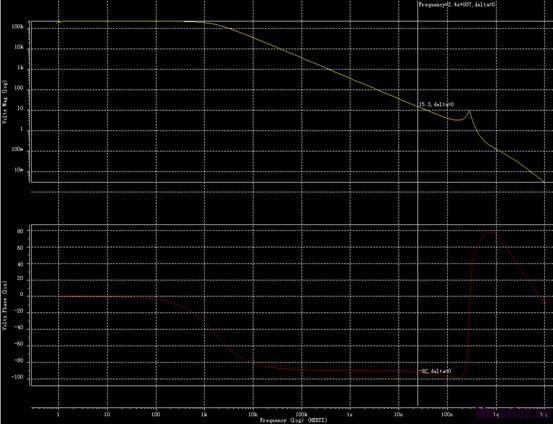

十分感谢你的回答,但是我有点不太清楚,运放设计的时候,增益上翘部分并不影响我的相位裕度,这样的上翘也必须消除吗,那这样的话可能要牺牲很大的带宽吧?刚才发的开环波特图不太清楚,重新发一遍

不知道大家碰到,在高频情况下,相位由于右半平面极点和左半平面零点,反而会变正的吗

看着是有复极点。

同样的疑惑啊期待大侠出现

我自己琢磨了下应该是前馈产生零点的原因吧这个需要你仔细认真慢慢调试的应该能解决的不过也不排除不能解决 我去年仿真了一个电路也是上翘一直解决不了

你好,十分感谢你的回答

我有两点疑问:

1:上翘最高点增益是10,然而我用在反馈系数为1/18的闭环回路中

2:在1000gig频率范围内,相位偏移正负都没有超过120°

这样的上翘,不至于出现这么明显的闭环阻尼情况吧?

应该带着外面的反馈通路仿开环啊,然后看开环0db 处的相位。你确定只是除以一个18这么简单?

你好,我是个刚接触模拟电路菜鸟,实际经验比较少,根据gray的书上知识的这样算的如果用在单位增益的闭环环路中,是必须看0db点的相位

然而在非单位增益情况下,是要看开环增益等于1/f点的相位的

我也菜鸟。我因为记得以前书上说,如果要测开环的OPamp的增益,必须把由于反馈网络而附加的等效阻抗加在opamp的输入输出上,就是保证环路断开前和断开后的状态相同。要么你算一下等效阻抗后单仿Opamp,或者整个环路用STB仿真试一下?

关注中

我最开始准备用开关电容作为负反馈的,后来不知道怎么仿如是换成了比较大的电阻作反馈,因为opamp输出级电阻不是非常大,反馈电阻对开环增益影响不是很大

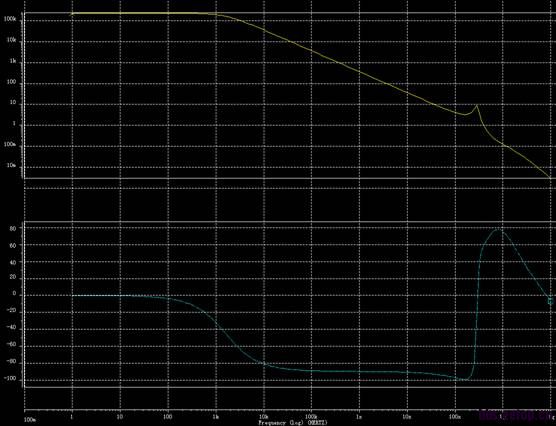

天仿了一个简单的单端输出两级运放,使用在增益为2的闭环回路中。这回开环没有增益上翘部分,但对应开环测得相位裕度,闭环的增益很是怪异。向大家请教,这到底怎么回事,怎么和书中预测差别这么大

要么把testbench也贴一下吧。还有最好y轴直接用dB20的坐标

就是你仿真的电路图,看看opamp外面怎么接的.比如vout的静态电压是怎么固定的

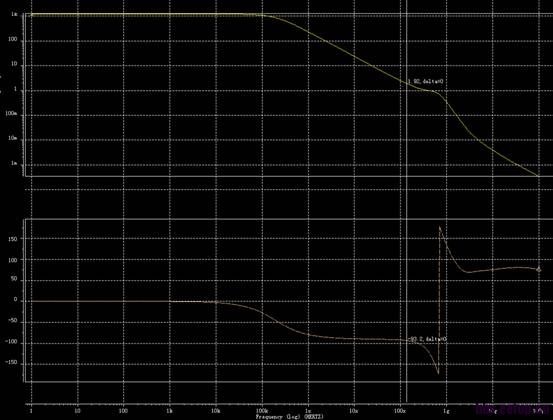

我用hspice仿的,下面分别外加的闭环反馈环路和共模负反馈电路

下午研究了一下fully output op-amp的test bench,看来我想的的太简单了,按照single output的来仿了

我重新仿一遍,然后把结果发上来

下午研究了一下fully output op-amp的test bench,看来我想的的太简单了,按照single output的来仿了

我重新仿一遍,然后把结果发上来

放假回来再弄了

看不懂!这个是什么仿出来的?

很怪异,用了两种testbench,仿真的结果和我最开始加的简单激励完全一致

下面贴出在hspice中的

第一种:

x1 vincm vindm vi+ vi- balun

vincm vincm GND! 1.17

vinac vindm GND! 0 ac 1

第二种:

e1 vi+ cm sig 0 0.5

e2 vi- cm sig 0 -0.5

vincm cm 0 1.17

vs sig 0 ac 1

请问有没有高手帮我解决一下这个问题

或者是我的testbench依然加错了,谢谢

hspice仿的

这么多。怎么下啊