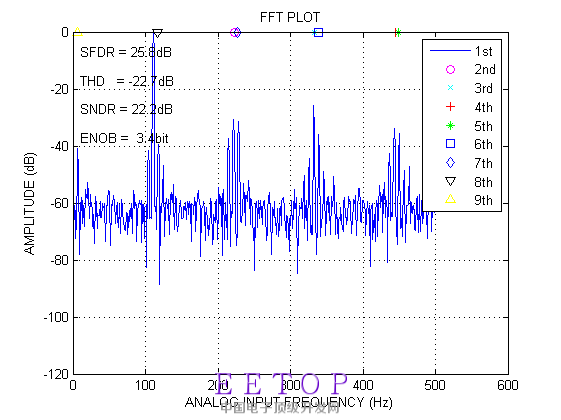

流片回来的10bit ADC测试

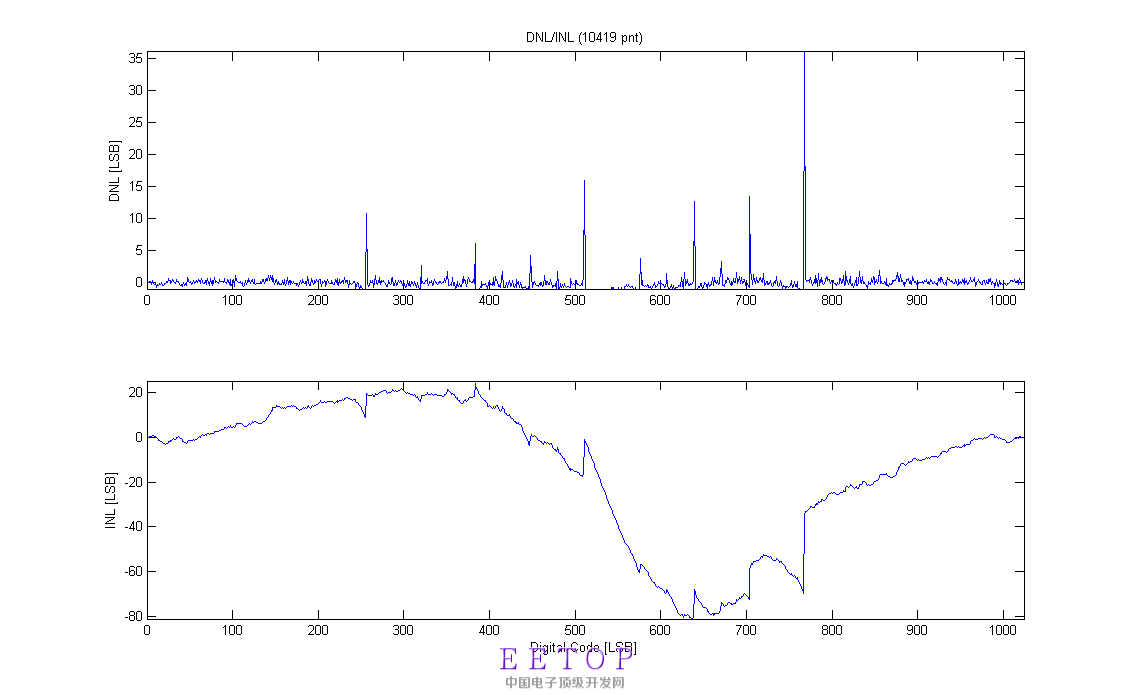

DNL/INL多差?

********************** DNL= - 1/+36 LSB

INL= -81/+24 LSB

**********************

以下两点建议:

1、你确定输入信号是OK的?我上家公司用FPGA产生signal给ADC(10bit的)做输入信号,我将此信号用800M逻辑分析仪采得的数据进行matlab计算。ENOB只有不到4bit。也就是说输入信号已经不行了,测得的ADC性能也就不准。2、加滤波器再进行测试,可能会好点。

mark,等结果

这是function错,建议你输入sine时候,把输出的10bit data贴出来,肯定有missing code或者大的jump/glitch。很有可能是logic timing issue,仿真看不出来

AD是SAR结构的;测试是未封装的芯片,电源直接利用泰克电源供电,输入差分信号直接利用函数发生器(14bit,网上搜索的)产生的,时钟信号是ARM开发板产生而且利用了电阻分压,自己觉得测试条件比较简陋。不知道是否对结果产生这么大的影响。自己觉得怎么也得测出6bit

AD是SAR结构的;测试是未封装的芯片,电源直接利用泰克电源供电,输入差分信号直接利用函数发生器(14bit,网上搜索的)产生的,时钟信号是ARM开发板产生而且利用了电阻分压,自己觉得测试条件比较简陋。不知道是否对结果产生这么大的影响

给输入几个固定电平,看看数据是多少。确定下是不是ADC的性能,应该是测试条件导致的这个结果

输入信号的问题吧,

你好,请问你这个DNL和INL ENOB是用怎么测试出来的呢,是用的什么方法呢,能透露下么?我手头也有个10bit 的ADC,测试结果看起来和你的差很大。

ADC的电源与VREF的去耦也要关注一下。

目前知道信号源的SNDR就比较差,也就4bit不到吧,不过我的频率比较低,现在没找到好的信号源,问安捷伦开放实验室那边说1khz以下的函数发生器产生的信号的thd达到-70dB以下比较难,现在是信号源不是很好找,不知道加滤波器能提高多少,请问前辈有什么建议吗

确实是信号源的SNDR就比较差,也就4bit不到吧,不过我的频率比较低,现在没找到好的信号源,问安捷伦开放实验室那边说1khz以下的函数发生器产生的信号的thd达到-70dB以下比较难,现在是信号源不是很好找,不知道加滤波器能提高多少,请问前辈有什么建议吗

目前测得信号源的SNDR就比较差,也就4bit不到吧,不过我的频率比较低,现在没找到好的信号源,问安捷伦开放实验室那边说1khz以下的函数发生器产生的信号的thd达到-70dB以下比较难,现在是信号源不是很好找,不知道加滤波器能提高多少,请问前辈有什么建议吗