一个2级cmos Op的笔试问题

我的看法是这样的,当输出增大的时候M10作为控制零点的电阻的阻值降低了,使零点值降低,降低了反馈系统的稳定性。

本人菜鸟,表达一下个人看法。希望大神出来给出更权威的解答

管子截止的话应该是产生波形失真吧,不会反正震荡,震荡还是因为相位裕度变低导致的吧

输出在1.5v时,作为调零电阻的M10阻值最大,零点频率拉低,相位裕度变差。

最优答案 增加M10

Z=gm6/(C*(1-gm6*R10))如果零点还是右半平面的,M10电阻增大,零点不应该变得更高频吗?如果变成左半平面的零点,相位裕度应该变好啊

Vout输出高电平时,输出+1.5V时,M10源端对应第二级输入端应该是低电平,Vgs10最大,所以M10沟道电阻最小,是这样吗

这样看来增大M6的尺寸来增大gm6应该可以吧

allen运放那一章课后题。

m10截止,没有miller补偿了,运放震荡。用个电阻替代m10

找到了,谢谢

M10不会截止的,栅电压为电源电压。原因还是输出高电平时M10电阻变小,以及M6跨阻变小导致RHP零点频率下降,使得相位裕度下降了

是,没注意电压

我觉得是这样的

which one, A, B, C or D?

输出电压变高时,NMOS的VGS下降,等效电阻变大才是

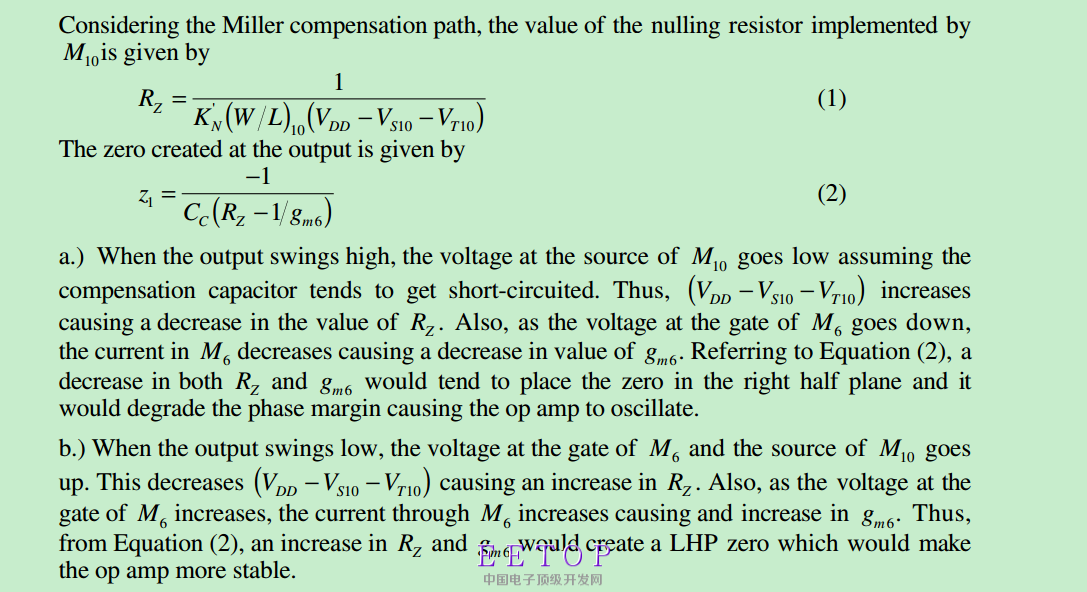

When the output swings high, the voltage at the source of M10 goes low assuming the

compensation capacitor tends to get short-circuited. Thus, (VDD −VS10 −VT10 ) increases

causing a decrease in the value of RZ . Also, as the voltage at the gate of M6 goes down,

the current in M6 decreases causing a decrease in value of gm 6. Referring to Z1=1/(1/gm6-Rz)Cc, a

decrease in both RZ and gm 6 would tend to place the zero in the right half plane and it

would degrade the phase margin causing the op amp to oscillate.

b.) When the output swings low, the voltage at the gate of M6 and the source of M10 goes

up. This decreases (VDD −VS10 −VT10 ) causing an increase in RZ . Also, as the voltage at the

gate of M6 increases, the current through M6 increases causing and increase in gm 6. Thus,

from Z1=1/(1/gm6-Rz)Cc, an increase in RZ and gm 6 would create a LHP zero which would make

the op amp more stable.

Increase gm6=> create LHP zero

讨论一下,基于这个BUFFER,输入0V的情况 和 输入1.5V的直流电平的情况 ,2个相位裕度如何?

M10源端应该是接电容那端,M6的栅与M10源端同向,输出高电平表示M10源端电位最低

对输入直流的情况,M10的电流为0,也就是VS10=VD10=VOUT,这时没有所谓的哪边高哪边低

可查的几个解释都是说输出为高电平时Rz等效电阻变小啊,按你的说法怎样解释才合理呢

你查的几个解释能罗列出来吗,最好有具体的过程。

按17楼兄弟的解释,应该是:在动态输入的过程中,输出正弦波由0升高到1.5V的过程中,M6的Vgs略降, 由于要对Cc充电且VCc电压几乎不变,所以有M10的Vgs略增大,这一过程中,也就是你所述的M10的等效电阻的变小,也就是你们解释的Rz变小导致零点变为右平面导致了相位裕度不足,这一过程中,可以说 Vs10<Vd10。

我的看法不同,由题目所给的波形可知摆率足够大,那么实际上这一过程中,Vgs6略降的程度非常小,并且,考虑Cc充电的过程中,VCc电压一定是增大的,且M10的W/L很小,也就是充电过程中,Vgs10一定不会增大反而减小,可以说M10的等效电阻一定会变大,也就是以离散dc工作点的视角来看这个过程,相位裕度反而是增大的;但是,到了这个过程后期,Vout几乎升至1.5V时,此时Vgs10减小到不足以开启M10的程度(计算一下此时的VT10,Vsb>0),那么M10的等效为断路,也就是米勒补偿路径消失,所以相位裕度突然不足,导致波形抖动

另一方面,这一过程中,充电Cc分流了M6电流,gm6下降在定性分析上也会降低相位裕度

输出1.5V,Vgs接近于1.5,要M10要关断,阈值电压翻一倍也才1.4V,可能这么大吗

从瞬态上看过程的末期,Vdd是2.5V ,vout是1.5V,压差是接近1V,还有 Cc两端的电压这时候是多少,这才决定了Vgs10的大小。而从DC上看Vout是1.5V的情况,显然M10的VGS10 比Vout是0V 时的VGS10更小, 等效电阻加大了, 反而优化了相位裕度

你这文章叫什么名字 方便上传吗

不是文章,Allen书后讲运放一章的习题答案,我也是在这网站上下的

ting hao

我以前看过一个贴子里的讨论,说时域的overshot肯定是由于相位裕度不足引起的,如果从这个角度来说,输出为1.5V时应该有相位裕度不足的问题http://bbs.eetop.cn/thread-612965-1-1.html这个贴子