理想 3bit DAC 里 Cadence Model Writer

时间:10-02

整理:3721RD

点击:

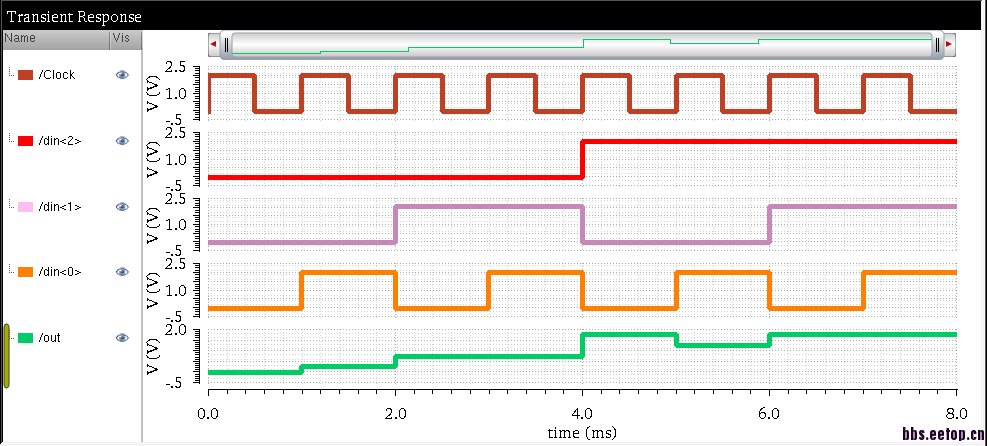

我设计 3bit DAC 里 Cadence Model Writer 但是当我测试这个, 结果是错误的

我写的veriloga代码如下,请高手分析哪里出了问题,谢谢!

// PARAMETERS:

//slack = Smallest time unit considered negligible for clock

// threshold cross event [S]

//tconv = Delay from clock edge to new output voltage [S]

//tfall = Output fall time for new output voltage [S]

//trise = Output rise time for new output voltage [S]

//vmax = Full scale analog output voltage [V]

//vmin = Zero scale analog output voltage [V]

//vth = Digital Input and Clock Logic Threshold [V]

//

`include"discipline.h"

`include"constants.h"

`define NUM_DAC_BITS3

module d2a_ideal (clk, din, vout);

input[`NUM_DAC_BITS-1:0] din;

electrical[`NUM_DAC_BITS-1:0] din;

inputclk;

electricalclk;

outputvout;

electricalvout;

parameter realvmax = 2;

parameter realvmin = 0;

parameter realvth = 1;

parameter realtrise = 0.1p from (0:inf);

parameter realtfall = 0.1p from (0:inf);

parameter realtconv = 0.1p from [0:inf);

parameter realslack = 0.1p from (0:inf);

parameter integer traceflag = 1;

reallsb, voffset, new_vout;

integer decimal_value;

analog begin

@(initial_step or initial_step("dc","ac","tran","xf"))begin

voffset = vmin;

decimal_value = 0;

lsb= (vmax - vmin) / (1 << `NUM_DAC_BITS) ;

if (traceflag) begin

$display("%M DACrange ( %g v ) /%d bits= lsb %g volts.\n",

vmax - vmin, `NUM_DAC_BITS, lsb );

$display(" offset %g volts.\n",voffset );

end

end

@(cross ( V(clk)-vth,1, slack, clk.potential.abstol)) begin

decimal_value=0;

generate i (`NUM_DAC_BITS-1, 0) begin

decimal_value = decimal_value + (( V(din[i]) > vth ) ? 1 << i : 0 );

end

new_vout = decimal_value * lsb + voffset;

if(traceflag)

$strobe("%M at %g sec. digitalin: %dvout: %g",

$abstime, decimal_value, (decimal_value * lsb) + voffset );

end

V(vout) <+ transition ( new_vout, tconv, trise, tfall );

end

endmodule

`undef NUM_DAC_BITS

我写的veriloga代码如下,请高手分析哪里出了问题,谢谢!

// PARAMETERS:

//slack = Smallest time unit considered negligible for clock

// threshold cross event [S]

//tconv = Delay from clock edge to new output voltage [S]

//tfall = Output fall time for new output voltage [S]

//trise = Output rise time for new output voltage [S]

//vmax = Full scale analog output voltage [V]

//vmin = Zero scale analog output voltage [V]

//vth = Digital Input and Clock Logic Threshold [V]

//

`include"discipline.h"

`include"constants.h"

`define NUM_DAC_BITS3

module d2a_ideal (clk, din, vout);

input[`NUM_DAC_BITS-1:0] din;

electrical[`NUM_DAC_BITS-1:0] din;

inputclk;

electricalclk;

outputvout;

electricalvout;

parameter realvmax = 2;

parameter realvmin = 0;

parameter realvth = 1;

parameter realtrise = 0.1p from (0:inf);

parameter realtfall = 0.1p from (0:inf);

parameter realtconv = 0.1p from [0:inf);

parameter realslack = 0.1p from (0:inf);

parameter integer traceflag = 1;

reallsb, voffset, new_vout;

integer decimal_value;

analog begin

@(initial_step or initial_step("dc","ac","tran","xf"))begin

voffset = vmin;

decimal_value = 0;

lsb= (vmax - vmin) / (1 << `NUM_DAC_BITS) ;

if (traceflag) begin

$display("%M DACrange ( %g v ) /%d bits= lsb %g volts.\n",

vmax - vmin, `NUM_DAC_BITS, lsb );

$display(" offset %g volts.\n",voffset );

end

end

@(cross ( V(clk)-vth,1, slack, clk.potential.abstol)) begin

decimal_value=0;

generate i (`NUM_DAC_BITS-1, 0) begin

decimal_value = decimal_value + (( V(din[i]) > vth ) ? 1 << i : 0 );

end

new_vout = decimal_value * lsb + voffset;

if(traceflag)

$strobe("%M at %g sec. digitalin: %dvout: %g",

$abstime, decimal_value, (decimal_value * lsb) + voffset );

end

V(vout) <+ transition ( new_vout, tconv, trise, tfall );

end

endmodule

`undef NUM_DAC_BITS

dac

嗨~想学习一下verilog a,LZ有什么资料可以分享一下吗?

我用modelwriter调出的rand_bit_stream也不能用,很奇怪

不是可以直接生成么