ee240 lecture 4中的问题

时间:10-02

整理:3721RD

点击:

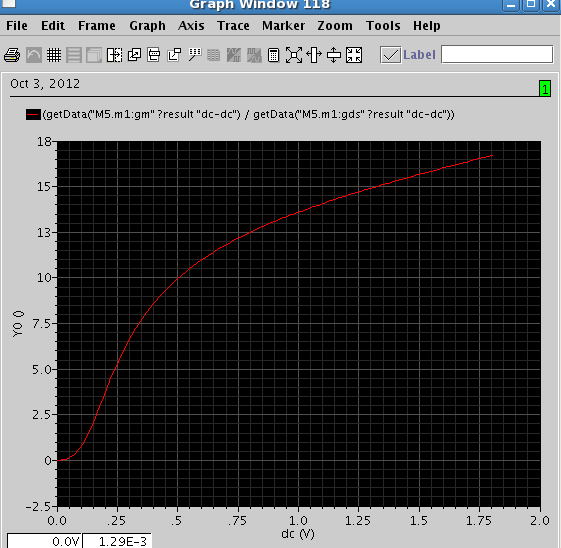

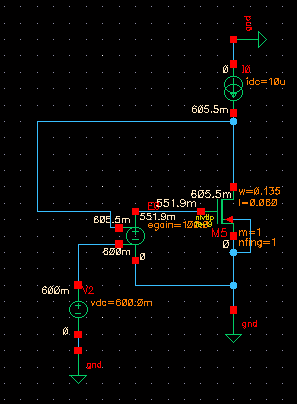

在ee240 第四课中,给出了这样的一个电路来测nmos当vds在一定范围内波动时的增益变化,如图device sizing1.然后接下来就说得到device sizing2的图,在vds比较大的地方,如1.2v之后,增益会下降,但是我自己搭了一个电路,却发现增益会一直在增加的,是否这两个图无关联?

测试電路和得到的曲线

自己顶一个

测试電路和得到的曲线

感觉和工艺库相关

应该是选的模型的问题,试试50nm的器件;2um的器件没有该效应(50nm和2um的器件模型不一样,不能简单设置沟道长度),50nm等短够器件因为DIBL,Impact ioning等效应,输出电阻会随Vds的增加而减小。仅供参考。

知道它为何下降我觉得就够了,看了几遍才听出来

你所用的管子Ids~Vds曲线翘尾巴是在vds多大时出现的?试试看在那个电压范围是否能看到这个现象。

我明白你的意思了,要产生这样的现象是需要足够大的vds的,而我之前仿的那个电压还不够,而且不同的工艺产生这样现象的vds也不一样,我用的65nm的管子,ee240用的好像是0.18um的管子,所以我开始以为尺寸小了,产生这样现象的vds会很小,但是实际仿真没出这样的结果,后来我增大电压,看到增益确实开始下降了,但是这个电压已经有5v多了,一般不會有这样的电压加到漏端,所以感觉自己做了没意义的事

同意所说的

thanks

小编可否把ee240的视频分享一下?谢谢了!