Cadence环境下PLL中chargepump模块的PSS+PNOISE仿真

求高手解答,不胜感激!

输出不能接iprobe,而是要接一个电压源,pnoise设置中,output选probe,将output probe instance选为这个电压源

您好,首先谢谢你的回答,还有个问题想请教你,应该是PFD+chargepump加在一起来仿真这个局部模块的相位噪声是吗?在这里我的鉴相频率也就是输入频率加的是2M,在做PSS+PNOISE时,PSS中的目标频率也就是

这个目标频率应该加多少呢?

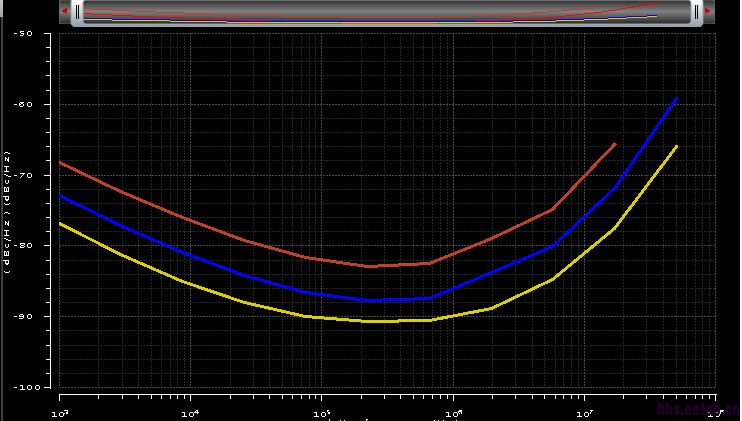

还有,当我把鉴相频率分别加为1M,2M,10M的时候,输出的相位噪声越来越小了也就是噪声性能越来越好了,不知道为什么?

但噪声性能最好的时候也就-91dbc左右,这算正常吗?怎么样才能减小chargepump的相位噪声呢?不胜感激!我用的是90nm工艺

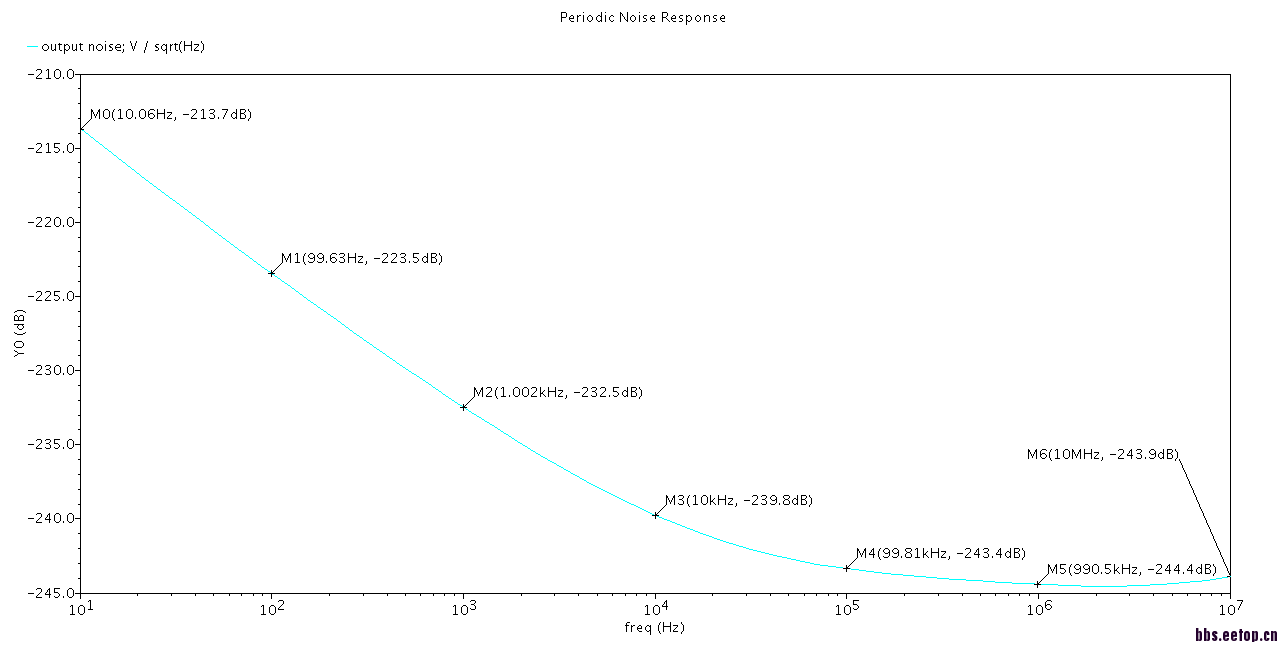

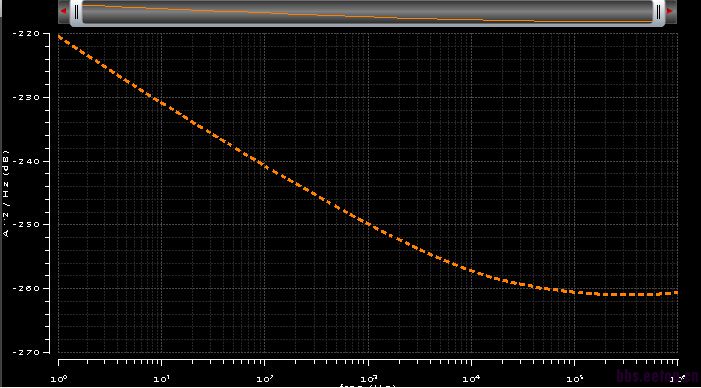

没错,PFD+chargepump加在一起来仿真CP的相位噪声。PSS的目标频率是电路中的最低频率,也就是PFD的输入频率,在这里应该是2M,这个地方你设置错了,因此下一个问题就无从回答了,先改过来再看结果吧。这个结果也不对,单位应该是dB,只看数值的话,是很差的,1k处应该-220dB左右,见图。

在调pnoise时,结束频率要小于beat freaquency的1/2,你这里设为1M应行了。噪声考虑跟电流镜是一样的,其实影响并不大,主要还是受电荷泵导通时间限制,上图是导通1nS的结果。

还有一点,PFD输入时钟不能用正弦,要用脉冲。

太感谢你了,你的这番话让我豁然开朗,这个问题困扰了我几个星期,再次谢谢!按照你说的步骤,我得到的输出噪声功率谱密度图如下

输出应该是db而不是dbc,这个时候得到的输出噪声不是相位噪声,而是输出的噪声电流功率谱密度,这个图中1K处的噪声为-250db,性能比较好,我仿真了一下锁定时的导通时间,大概0.5ns,我估计是这个值比较小的缘故才使得噪声好,但是这个小的导通时间会导致PFD出现死区吗,导通时间至少要大于多少才可以避免出现死区呢,是不是不同的工艺有不同的要求和限制,我用的是90nm工艺的,这个导通时间最小值可以仿真出来吗

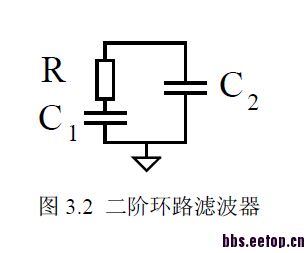

还想请教你一个问题,PLL每一个模块都可以用PSS+PNOISE仿真其输出噪声,但请问环路滤波器这一模块怎么仿真其输出噪声呢,

要看pfd输入完全对齐的情况下,电荷泵有没有导通(充放电同时导通)。比如电荷泵电流=100uA,0.5nS下充放电均能达到100uA,就没有死区,一般要留有裕量,或设置控制位。关于噪声,与电流大小也有关,我的是100uA,如果减小,应该会变好(闭环后则反过来)。你的电流是多少呢,有没有完全打开?

这个我没有单独做过,不好回答,感觉没什么必要。如果非要看,试试跟电荷泵一起,看电压噪声。

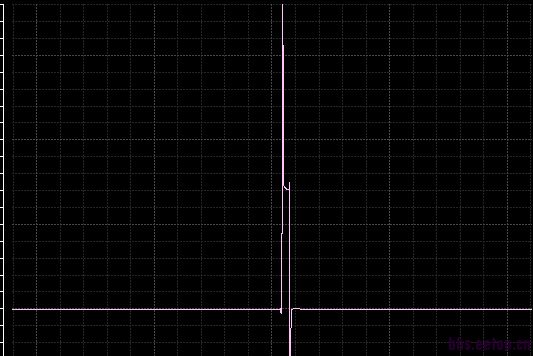

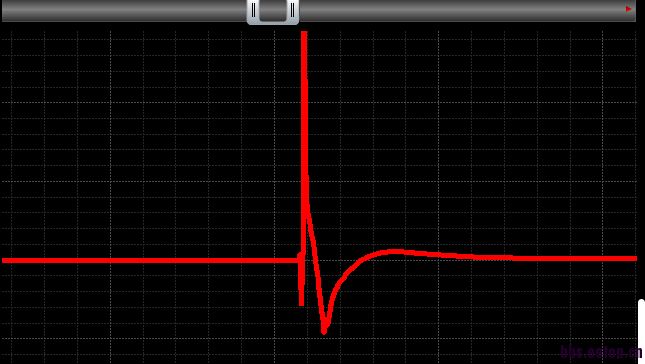

我电流是80uA,电流越大,CP对输出的噪声贡献越小,但会使得电容很大占用芯片面积,并且功耗大,这是一个折衷问题。导通时间刚开始只有0.5ns的时候,开关管确实没有完全打开,但我把导通时间延长至1.3n的时候,在这段时间通过开关管的电流出现这样:左图为充电电流,右图为放电电流,我很好奇为什么瞬间会有这么大的短时间的电流脉冲,并且充电电流瞬时脉冲比放电电流大得多,然后我测了一下CP的输出看是否有输出电流(理想情况下应该不会有电流流出),实测结果如右图第三张,你有出现过这样的情况吗?

脉冲是电容耠合引起的,要设法减小,设计、结构、版图等。理想情况不可能达到,但要尽量接近,上面这个图是挺差的,但能做到什么程度,该做到什么程度,我也不清楚,还有,充放电过程要放在同一张图上,便于比较。动态过程的设计是电荷泵设计关键,多下功夫吧

你说的“电容耠合”指的是电容耦合吗?,据我所了解的,时钟馈通效应应该就是指的是开关信号通过栅漏电容的耦合,是这样的因素导致了充放电电流上的过冲吗?我以前做电荷泵,在调试其性能时,都只是做了所谓的静态匹配,即保持充放电电流源的上下两个开关一直完全打开,然后扫描输出电压,使得在我需要的输出电压范围内充放电电流相等即匹配,动态设计的过程我看了这么多论文,好像都没怎么提到过。在电荷泵设计的过程中如何去减小这个短时间的电流过冲呢?你有没有相关论文或资料,或者提供一下你的经验?,感激不尽!

下图是我把导通时间加大之后的充放电电流,我现在把他们放在一起了,其中白色的线表示上面的充电电流,红色的线表示下面的放电电流,我很好奇为什么红色的线会到达稳定的慢一些?也就是为什么放电电流在完全导通之前有一段慢慢上升的曲线而不是突然直线上升?

1.取决于你lock状态下,CP输出电压多少。

2.开关管和电流镜管放置的位置交换一下,你会发现打开瞬间就没有那么大的过冲了。这个问题也需要权衡,交换后电流打开就会慢一些。

对的,时钟溃通引起的,动态过程的资料确实不多,有也不一定靠谱。还是要多思考啊,像知道了你的电荷泵原先没打开,噪声就得重仿了,不知你做过没有

我做过了,因为导通时间加大了,我知道噪声电流肯定会变差一点,但还好,在我所要求的范围之内

我刚刚思考了一下,我个人觉得这个电流过冲好像也没什么大的影响,虽然这个瞬时过冲电流很大,但是维持时间相当短,所以对LPF输出电压的影响大不,因为输出电压的变化是因为充放电电流对电容的积分,积分值是与时间成正比的,所以输出电压变化相当小。你的观点呢?

这个我也不清楚,还在摸索

你好 请问你所说的锁定时的导通时间是怎么仿真的呢?谢谢!

为什么交换后打开会慢一些呢?

PFD输入频率完全相同的脉冲源,看PFD输出的UP或DOWN信号出现高电平或低电平过冲的时间,这个导通时间就是锁定时的导通时间,你了解锁相环的话这个概念应该很清楚

LS 你的输出纵轴为电流的噪声输出,我在仿真时,plot的是V/sqrt/hz的纵轴?请问你是怎么做到的?

另外,我看有的资料上的输出横轴为10K~10M ,然后我看你的那个输出结果中,为1~1M。我的PFD的输入时钟为25M,但是仿真出来的结果,输出噪声 才-140db,未能出现你们仿真结果中的-220db左右,

hghgfhgfhgfhgf

输出噪声 才-140db的话 就是CP的匹配做差了 上下电流源 静态不匹配 是照成 你的问题的主要原因 解决方法 是改变CP结构 可以到IEEE上收一下很多 但大同小异 基本使用复制电流支路的思想

谢谢 我发现是我的仿真方法有问题的 已经更正了

LZ问一下你单独仿真PFD+cp的时候输入两路信号用的是Vpulse?Pnoise里设置的input怎么选的?

两路输入同时接vpulse,PNOISE中的input选为none

请问小编仿真出的cp结果是哪种幅值呢

输出应该是噪声电流的功率谱密度,单位是电流的平方每赫兹,如果要把这个曲线送到MATLAB去噪声拟合,应转化为dB的单位

开关管W/L减小,可以降低这个过冲,不过导通时间也会变大,需要折中。