hspice 后仿问题

网表看是没什么错,仿真你是没跑动报error,还是跑起来了但没波形?

试试这个检查:

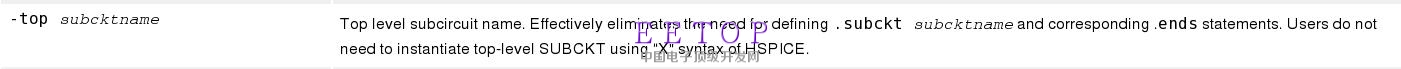

后仿网表的顶层电路是子电路定义的,看看前仿网表的顶层电路是不是子电路定义的。如果前仿网表没有子电路定义,那就需要在后仿的命令里面加一个“-top subcktname”,把顶层电路的子电路定义去掉。

没有报错,就是不出波形..

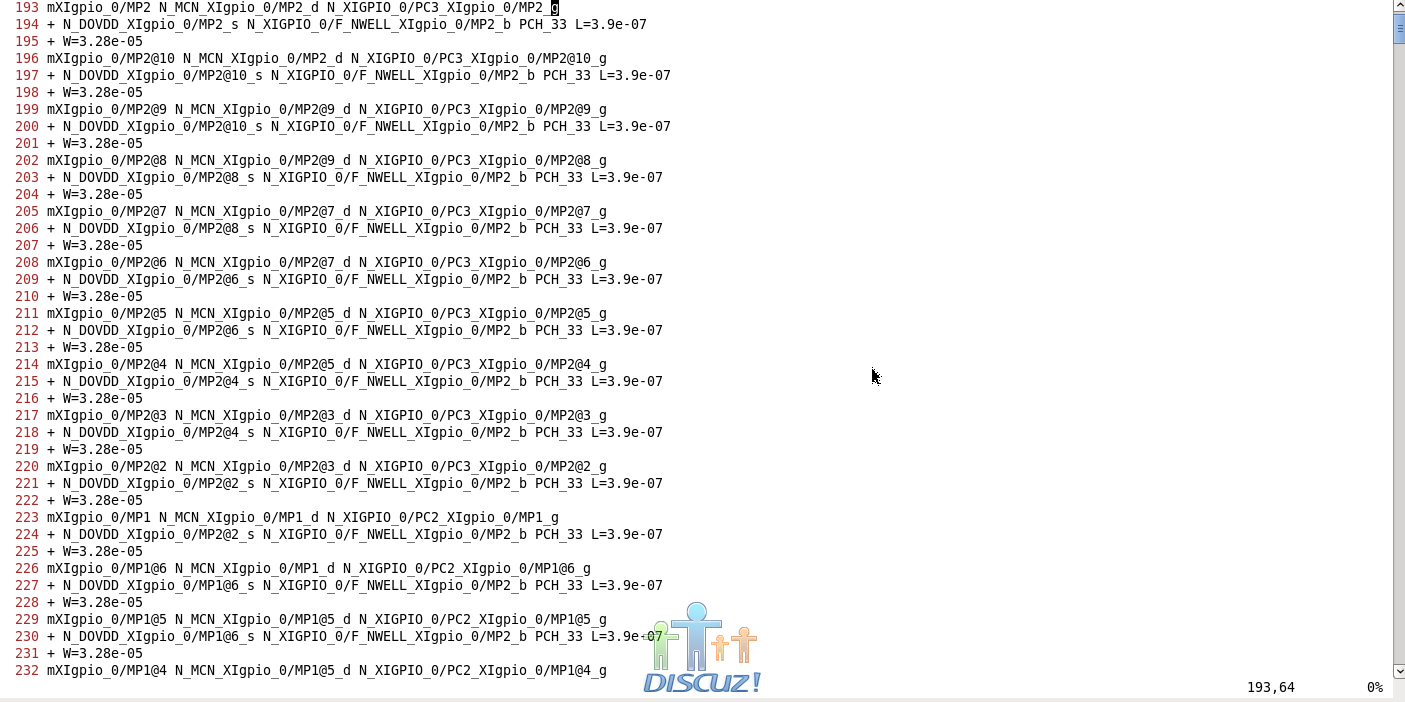

我把我的sp文件贴出来,您帮我看一下,同样的文件,我只是把后仿的网表,写成前仿的.net网表,就可以跑了,是不是我哪里设置的问题呢?sti.vcd2pwl里面全部都是激励

这个是前仿的网表,前仿的网表,感觉是子电路定义的,后仿的网表,感觉和前仿的网表定义不太一样,您刚才说的那个方法,可以具体一点吗?这个“-top subcktname”命令,是直接跑后仿的时候,直接加到命令里面就可以吗?是hspice -top subcktnamexxxxx.sp >xxx.lis,但感觉这样不是hspice的命令呢?可以具体说一下具体咋样做吗?谢谢您了

我把前仿的网表贴出来了,前仿里面应该有子电路电议的,您说的那个检查,在后仿的命令里面加一个“-top subcktname”,咋样加呢?hspice --top subcktname xxxx.sp >xxxx.lis,这样感觉命令不太对,可以具体说一下吗?

我把前仿的网表贴出来了,前仿里面应该有子电路电议的,您说的那个检查,在后仿的命令里面加一个“-top subcktname”,咋样加呢?hspice --top subcktname xxxx.sp >xxxx.lis,这样感觉命令不太对,可以具体说一下吗?

我把前仿的网表贴出来了,前仿里面应该有子电路电议的,您说的那个检查,在后仿的命令里面加一个“-top subcktname”,咋样加呢?hspice --top subcktname xxxx.sp >xxxx.lis,这样感觉命令不太对,可以具体说一下吗?

管理员为啥不让我回复啊,需要审核是什么鬼啊

我把前仿的网表贴出来了,前仿里面应该有子电路电议的,您说的那个检查,在后仿的命令里面加一个“-top subcktname”,咋样加呢?hspice --top subcktname xxxx.sp >xxxx.lis,这样感觉命令不太对,可以具体说一下吗?

我把前仿的网表贴出来了,前仿里面应该有子电路电议的,您说的那个检查,在后仿的命令里面加一个“-top subcktname”,咋样加呢?hspice --top subcktname xxxx.sp >xxxx.lis,这样感觉命令不太对,可以具体说一下吗?

我把前仿的网表贴出来了,应该是有子电路定义的,您说的加那个命令,是什么意思呢?后仿的命令里面加一个“-top subcktname”,把顶层电路的子电路定义去掉,subcktname是具体的名字吗?还是直接就是hspice -top subcktname xxxx.sp > sss.lis,这样感觉命令不太对呢?

之前我也遇到过类似的问题。你把提取出来的参数文件复制到.sp网表文件里面,不用include试试,我的就是这样成功了

好像不行,我刚试了一下,那网表有100多万行,我全部复制到了.sp网表里面,然后把原先的.includexxxx.netlist去掉了,感觉和原先的一样,如果直接用hspice xxxx.sp的话,不出结果,不报错,如果使用hspice xxxx.sp -top subcktname的话,就开始说 nchpchnch_33 pch_33找不到,但是这些都在我的库里面呢,并且我包含的应该没问题的,只要把后仿网表换成前仿网表,就一切OK了,真不知道哪里问题....

输入的信号波形也没有吗?

有输入信号波形,就是没输出的,一度怀疑网表不对的,我在前面把后仿网表也贴出来了,感觉也没啥问题,启动hspice的命令还是hspice xxx.sp的吗?我要是这样启动hspice的话,就不会报错,输入的波形都有,但没输出的,如果启动命令是hspice xxx.sp -top subscate name的话,就开始报错,说是nchpch找不到,但我的.lib里面是有的,并且包含的应该也没问题

输入波形是有的

你的问题,多半是因为后仿的网表的库不对,你用的是前仿的库,你确认一下库文件吧

subcktname是你的后仿顶层的子电路名,在后仿网表的

.subckt xxxx

可以看到,其中xxxx是子电路名。

嗯,用您说的这个方法跑起来了,谢谢