运放的Loopgain phase反过来了,非常迷惑,需要高手解答

时间:10-02

整理:3721RD

点击:

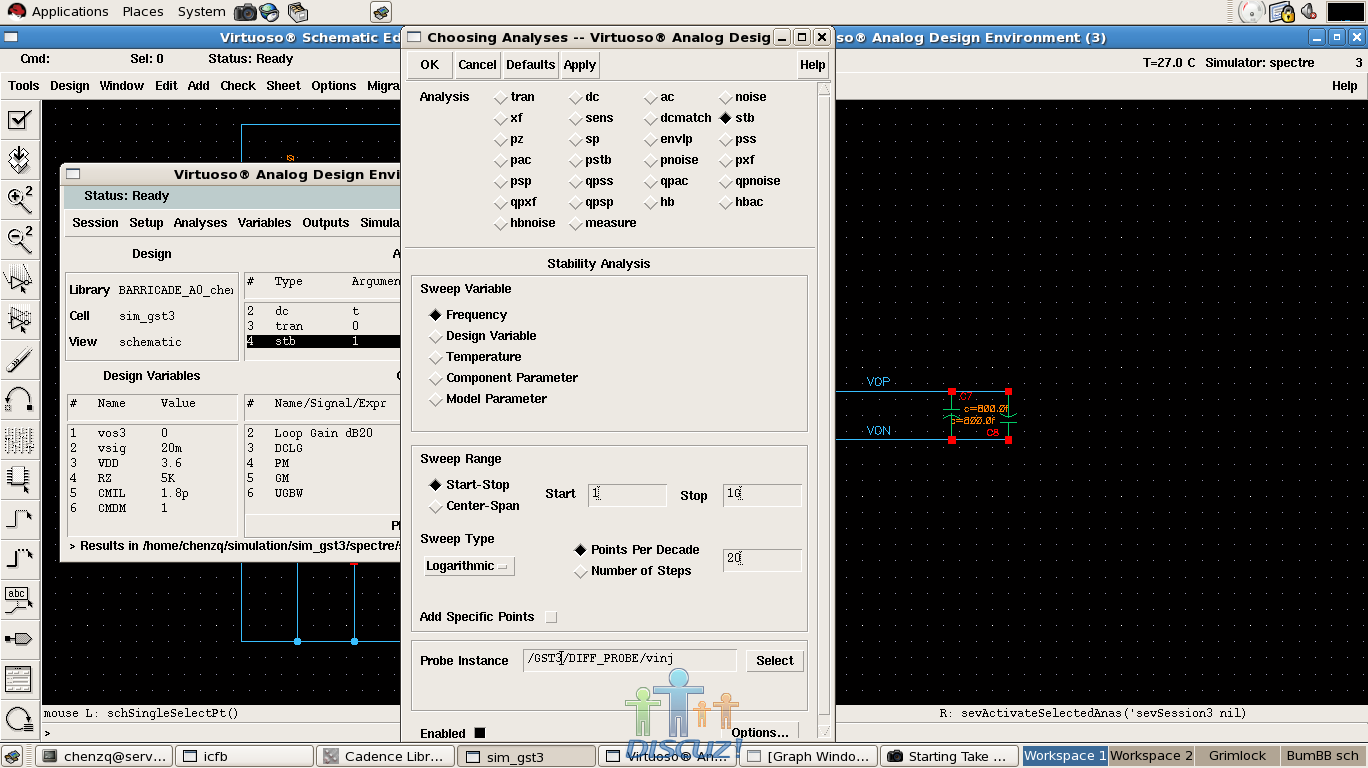

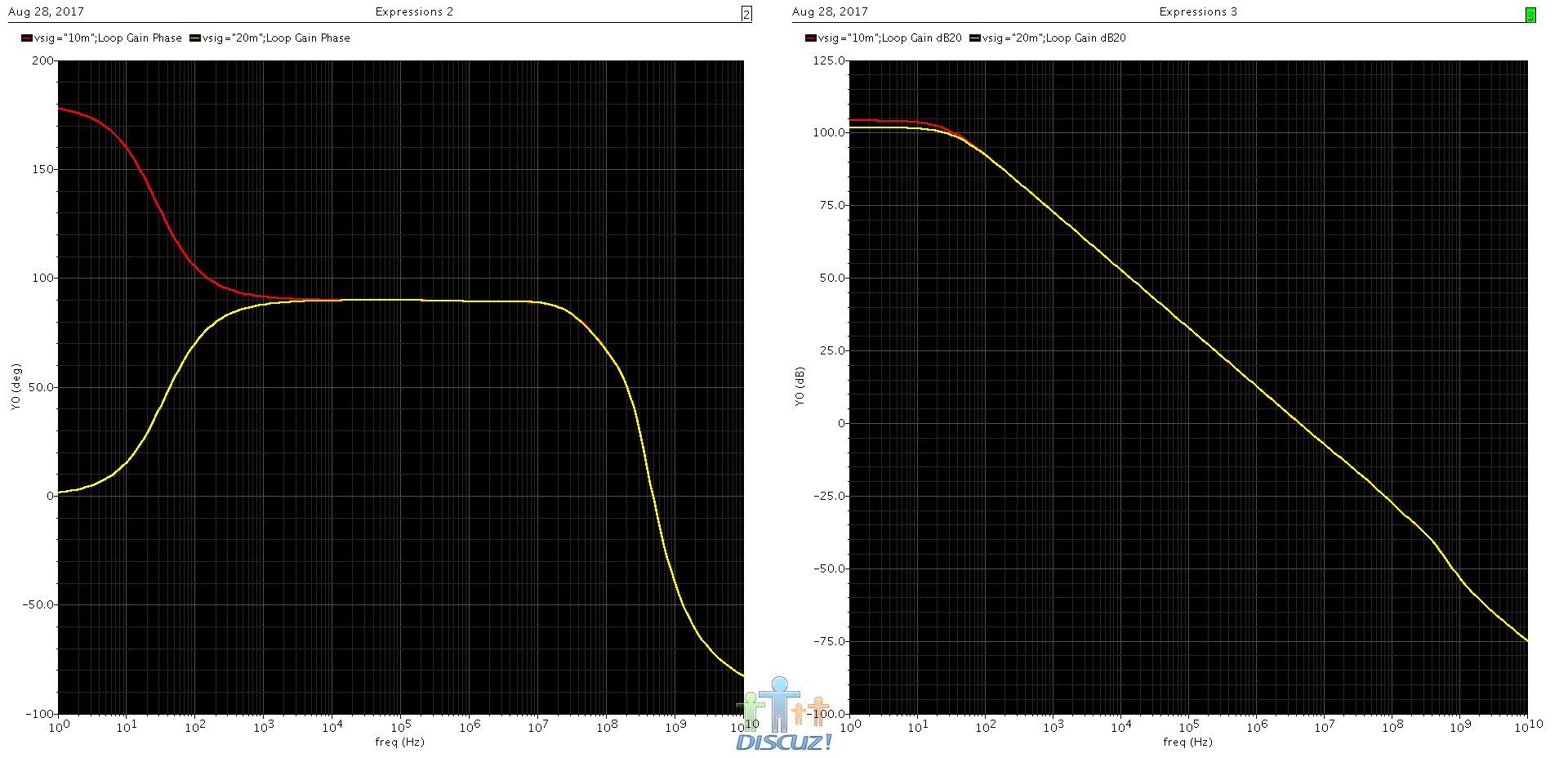

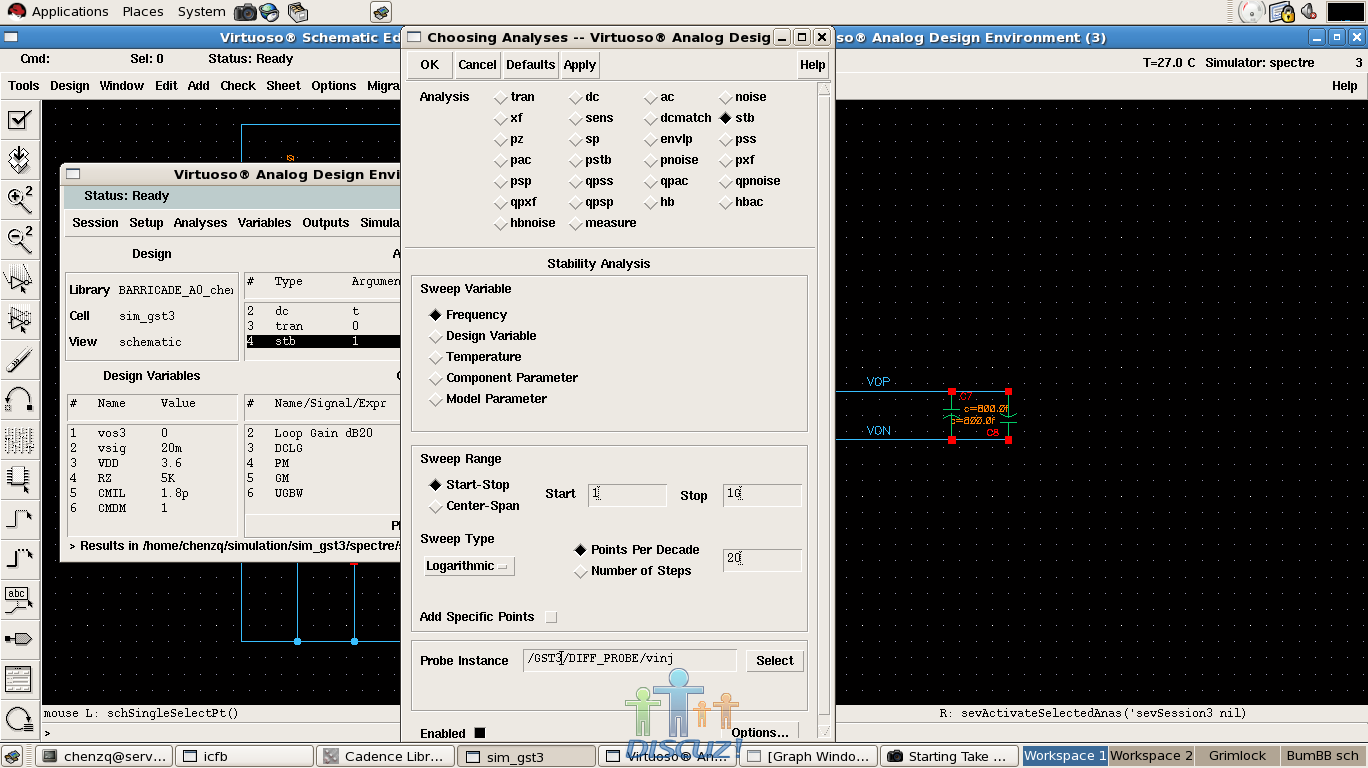

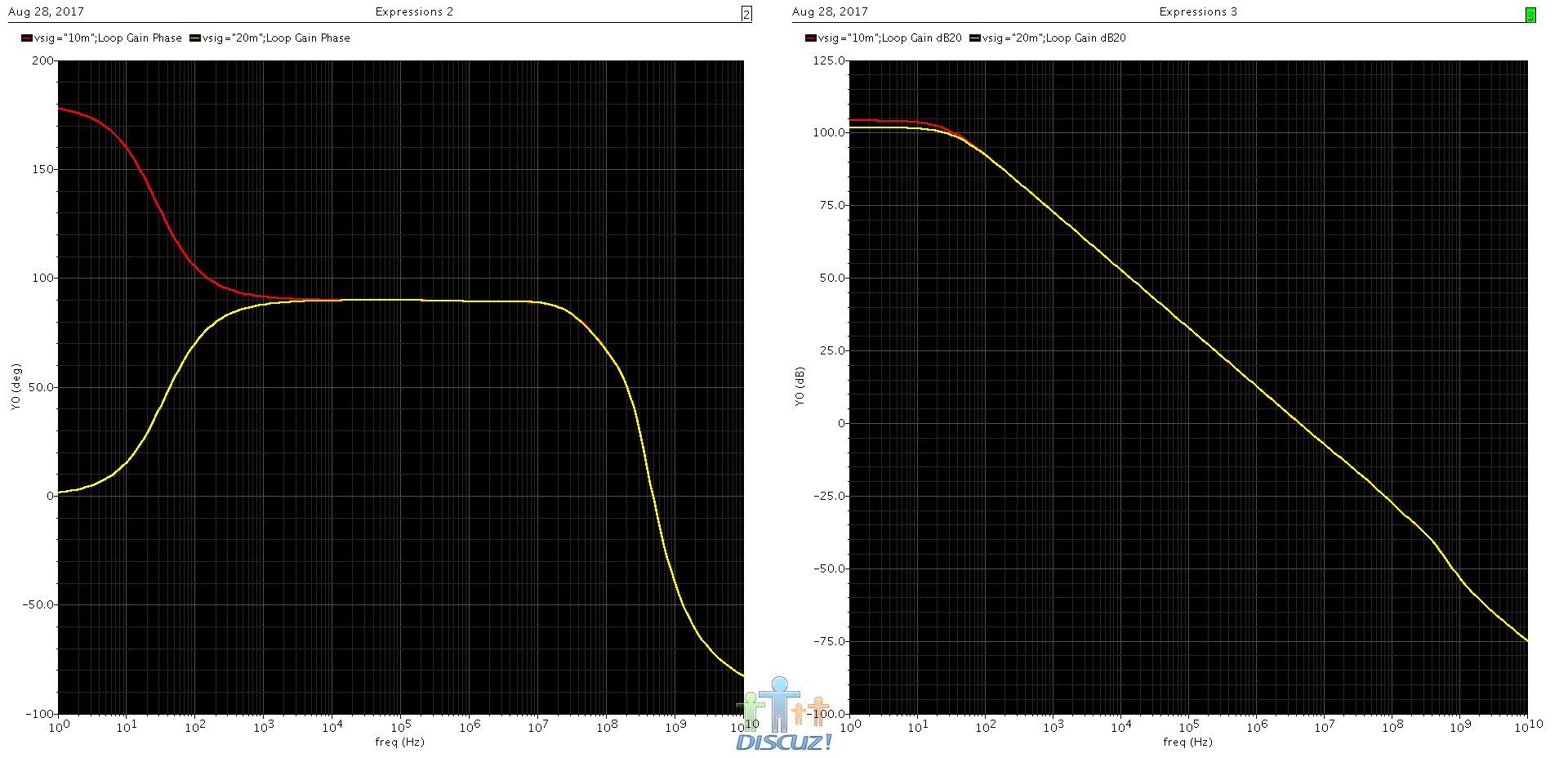

我有一个简单的运放,是伪差分电阻反馈,内部opamp是简单的两级放大器。用stb和cmdmprobe做稳定性仿真。现在cmdm=1也就是共模情况,现在20mV的差分输入时,loopgain phase变成从0开始,不符合常理,现换成10mV差分输入,这个phase看上去就是对的了。注意DC点都是正常的,反馈也不可能接反,transient响应也正常,不是那种低级错误。另外改变VDD电压也能让相位突然变正常或突然反过来。真的很困惑!之前在class AB运放中也碰到过类似相位倒过来的问题,当时就不了了之,有兴趣可以看这个帖子,总之我们同事都无法解答这个问题,希望有碰到过的人指点一下。http://bbs.eetop.cn/thread-290155-1-1.html

http://bbs.eetop.cn/thread-625723-1-1.html

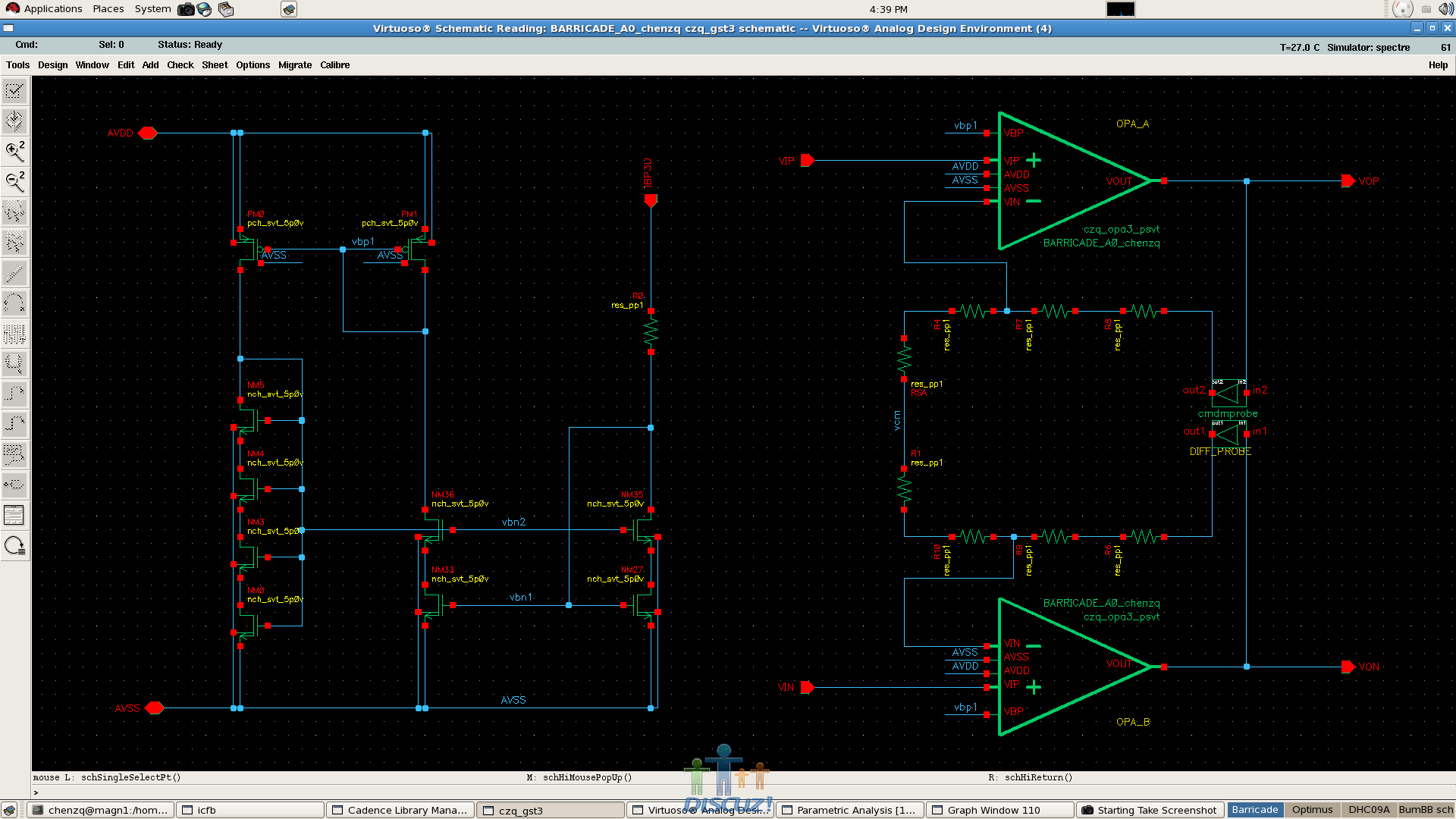

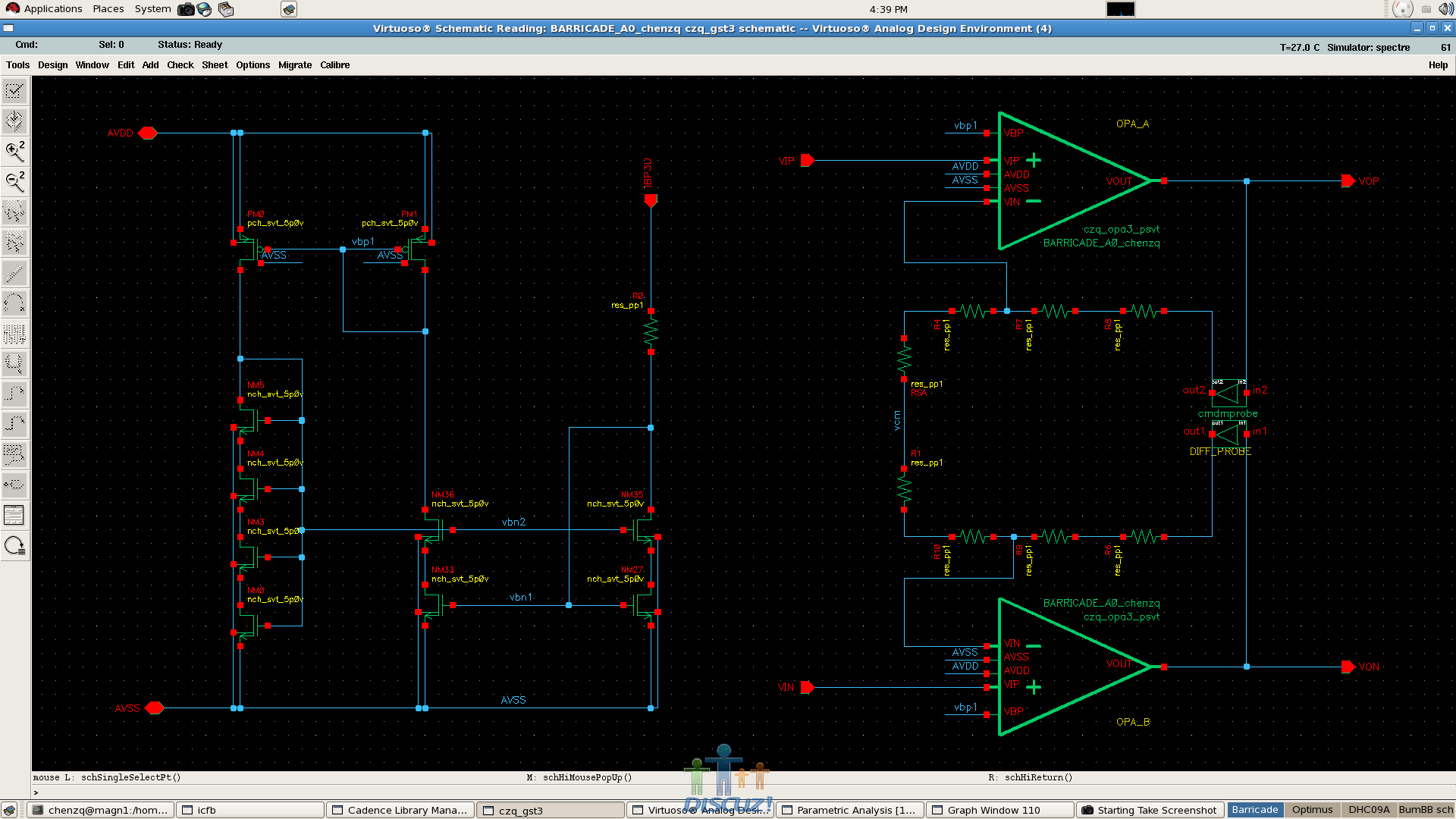

电路贴图:

http://bbs.eetop.cn/thread-625723-1-1.html

电路贴图:

单凡遇到phase从0开始的 我遇到的里面都有一个正反馈嵌套在里面

用ac仿真断开环路的方法,就没问题了。但真的不知道为什么,我感觉以后稳定性都不敢用STB仿真了,这个结构也很明显,没什么正反馈

我之前讲错了应该说是两个负反馈环路嵌套在里面AC是简单粗暴的断开忽略了断开引起的环路影响 需要人为的经验判断STB基于TIAN's method本身理论就考虑了这些因素 不能说你AC是对的就否定STB