电流模bandgap环路稳定性问题

时间:10-02

整理:3721RD

点击:

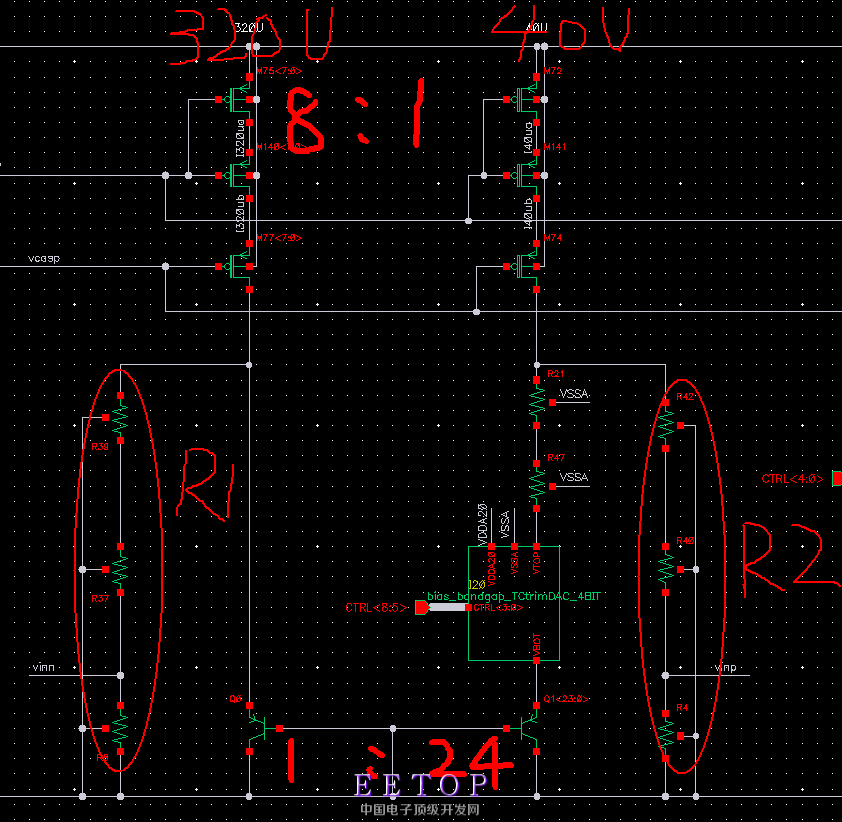

请教各位大大关于BG环路稳定性问题,如图所示

这个bg用于给14bit pipeline提供reference,对噪声要求比较高,所以电流相对比较大

左路电流镜与右路电流镜电流之比为:8:1,左右两个pnp的面积比为1:24

理论上我为了流过两个pnp的电流成比例,那么左侧电阻串R1与右侧电阻串R2比应为1:8,这样流过两个pnp的电流才会是8:1,但是当我将R1电阻值设成R2的1/8时,这时候便出现了环路稳定性问题,环路增益变成了负值,右侧电流镜电流变成了nA级别。

当我将电阻比例从1/8增大到1/7时,继续增大到1/1也是稳定的,虽然这时候Iptat已经不是Iptat了,我推过整个环路的环路增益公式,也没发现问题,不知道是哪里出现了问题。

另外这个BG中用的op为折叠式共源共栅运放,p管输入,最终bg输出电压为700mV.

虽然当时流片时用的R1:R2=1:1,测试也没问题,但一直对这个比较疑惑,请各位大大指教

补充:R2数值在35K左右,假设R1:R2=1:8,那么R1=1/8*R2, 工艺为tsmc 55nm

通常这种BG是有个负反馈环路在里边的,我觉得不能乱调电阻,很有可能是你调完电阻之后,这个环路变成了正反馈了,所以电路起不来。还有一点,我觉得你搞了这么多的比例,什么1:8,1:24,说实话我都晕了,做电路尽量简单,你要大电流可以用其他方法做一个大电流,不要用这种比值什么的,很容易晕,也很容易错,因为反馈环路会变的。

整个电路的工作原理搞清楚了吗?

既然公式都会推,感觉对原理还是没有理解啊

我自认为理解没问题,这个结构出自Leung 2003的JSSCC,只是有所变形,这个电路是公司前同事搭的,我后续做了优化,我只是没想明白他这样设置比例的初衷是什么,那请说说您的理解

环路稳定性问题,环路增益变成了负值,右侧电流镜电流变成了nA级别。?

这么说好像不是稳定性问题,好像是静态点没偏置好。

毕竟不是负反馈变成了正反馈

文章能否发出来,看看

简单来说公式成立 是基于负反馈 产生Delta Vbe /R Delta Vbe 是怎么产生的 基于Ic相等, Ic怎样才能让它相等

公式只是公式 不理解公式背后 需要哪些条件才能让它成立所以才说理解了?