关于折叠式共源共栅的两个问题

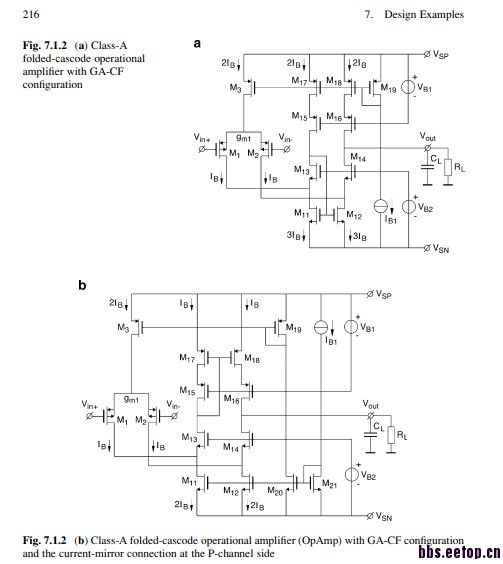

问题1.这两种运放的区别在哪里?三森书上讲到了高频特性会有差异,Huijsing在7.1节讲到会有noise和offset的差异,但是我理解不了,看不懂,这两种运放哪种在工业界用的更多?哪位大牛能结合自己经验谈谈这两种运放的区别和设计时要注意的细节问题,感激不尽!

问题2,折叠是共源共栅两条支路的电流是如何分配的?个人认为要考虑的细节是1.转换,2.噪声&失配,3.增益。大牛们怎么认为呢?

呵呵,这是个好问题。

两种都很常见,用哪种取决于系统的要求。

在对offset要求不高的时候我用a更多。

1、A最大的好处是PSRR明显优于B。很久没看书了,不知道sansen所以高频特性差异是不是指这个。

道理上,在高频段,高端的p cascade current source ron会变小。电流会随着VDD有变化,但A左右支路

的电流通过下端N mirror后,在输出是相减的,所以高频段的PSRR A》B

2、OFFSET B要稍优于A

因为B的输入对管尾电流是不影响offset的。只取决于input pair,P mirror和N mirror本身的match

但A还多了尾电流和P mirror之间的 match

3、对于noise ,比较的前提是电流一致,input, P ,N的 GM一致

在这个前提下,应该说相差不大。但一定要比也是A烧大一些。因为相对来说,A的下N管由于diode连接的关系,到输出的gain相对小些,所以折算到输入的等效输入噪声稍大,只是稍大。

关于具体怎样分配,要把应用系统的要求吃透,也不是每个指标多要做的很好,这个是通用单片opamp的要求,在大的CMOS集成系统里,系统需要什么才是最重要的,比如只要做一个VtoI转换,可能只要注意gian稳定性,PSRR就足够了,其他的不看也没关系。

好高深啊,看来我功力还是不行,得好好琢磨一下您说的话。谢谢O(∩_∩)O

PSRR有正负,你好像只考虑正PSRR了吧

如果是双电源系统确实有正负PSRR的问题。只是现在的CMOS系统绝大部分都是单电源,我工作经历涉及的也都是单电源。由于大家都是以大地为参考电位,就没有负psrr了,如果地动了,所有的信号绝对值也都变了。

单在工业控制上,还多都是双电源系统。比较遗憾一直做消费类产品,如果有做这方面的兄弟,可以给大家讲讲如何考虑。

能不能再详细解释一下,为什么差分对管的微电流和套筒的电流不match时,会产生offset?

感谢jeff_zx 的详解,学习了

我问你一个问题,folded cascode opamp 的CMRR要好于telescopeic cascode opamp的CMRR,直观上用电流cancel可以分析出来,是不是?

首先,如果你把CMRR只是理解为公式中的acm/dcm是没有什么用处的。

在实际中,CMRR的意义在于一个运放放大信号是共模或者说DC bias不断变化时,输出的信号的offset是否变化。

举个简单易懂但不严谨的例子,一个运放做单位增益buffer,VDD是5V。当输入是2.5V时,输出是2.499V,输入是1V时,

输出是输出是0.989V,但输入是3.5V时输出是 3.51V,但输入大于4V是,如果不是R2R结构,可能就不能正常放大了。

这个其实就是CMRR再实际中的表现。这是举个例子,不严谨。

实际中,说道CMRR不能忽略offset ,mismatch。有时候输入共模范围比CMRR更有意思。

telescope再这方面有天生的缺陷,没办法的。

也就是说如果CMRR为无穷大,那么输入失调电压就不会随共模输入电压而变化了?也就是说CMRR是衡量输入失调电压变化量的一个指标.对吧

如果频率很高时CMRR下降,那么是不是可以说频率很高时输入失调电压随共模输入电压的变化而变化的越大呢?

也就是说如果CMRR为无穷大,假设运放增益不会随共模输入电压而变化(实际上是不会变的due to lambda随vou而变)那么输入失调电压就不会随共模输入电压而变化了?也就是说CMRR是衡量输入失调电压变化量的一个指标.对吧

如果频率很高时CMRR下降,那么是不是可以说频率很高时输入失调电压随共模输入电压的变化而变化的越大呢?

前辈,我对您这个观点有点想法“在实际中,CMRR的意义在于一个运放放大信号是共模或者说DC bias不断变化时,输出的信号的offset是否变化。”。比如两个运放,接成单位增益buffer后,第一个运放,输入电压1V,输出电压是1.1V,输入电压从1V变化到2V这个过程中,输出电压从1.1V变化到1.1000001V。第二个运放,输入电压1V,输出电压是1.0001V,输入电压从1V变化到2V这个过程中,输出电压从1.0001V变化到1.0005V.第二个运放的输出信号的offset变化要比第一个大得多,所以第二个运放CMRR远大于第一个,是吧?但是如果这两个运放里所有管子都是匹配的,这样CMRR还是要用Avdm/Avcm来表示,第一个运放的Avdm比如30dB,Avcm是-50dB,CMRR=80dB,第二个运放的Avdm=100dB,Avcm=20dB,CMRR还是80dB。这样一来,两个运放的CMRR是相等的!我的分析哪错了?

厄。我说过这个例子不严谨,因为没有完全的区分共模和差模信号。公式是这样的,所以你这样算是没有错误的。

但有些脱离实际,在实际中,你op的gain如果只有30dB,整个信号放大精度1%都不到,又怎么会在意共模的增益是多少呢?

但如果你的差模增益很大,信号放大的要求又很高,CM就会成为拖累。

这个有点类似noise floor和SNR的关系,有时候noise floor绝对值是多少更重要。因为noise 代表了op本身的能力,SNR却可以借助

VDD的提高而增大。

总之,在实际的design中,至少一半以上的时间不用太care CMRR,重要的是输入共模范围和input offset。除非你从事的是高精度单片

通用运放的设计。比如IA这样的。

offset 随共模输入电压的变化而变化是不是会引入非线性?比如采保电路

呵呵,严格意义上说不一定,要看这个变化是线性还是非线性的。说到采保电路的时候就复杂很多了,要结合系统和应用分析。

那为什么有时候需要高CMRR指标?减弱offset对共模输入电压的依赖到底是为了什么?

严格按你说的,两者CMRR是一样的。

你的分析错在,你的1.1到1.0000001跟你给出的增益根本不一样。其实Avcm到了20dB, 输入从1V变到2V时,输出差不多也11V的样子了吧,你说呢?

数据有错了。为什么有时候需要高CMRR指标?减弱offset对共模输入电压的依赖到底是为了什么?

你在这个问题上有些钻牛角尖了,move on 吧

脱开实际的design和系统的需求,讨论这些就有点蒋公地图开疆的感觉了。

开个玩笑,很多时候还是要自己动手多做做simulation

难得看到eetop上有讨论帖,先赞一个!

Some comments for your information

1. Sansen的书上在slide 0732中说到:“fig (a)比fig (b)的对称性差一点,因为(a)的输入对管的负载会因为M13和M14的接法不一样而不同,但我再指出一点,从M14的source看上去并不是1/gm14,应该是(Rcasp+ro14)/(1+gm14*ro14) ,通常Rcasp会比ro14大,所以不能简化成1/gm14;从M13的source看上去的电阻可以推推,我也没推出Sansen书上说的那样结论”

2. 我觉得看应用来选用哪种结构,第一种NMOS self bias,M11的gate电压一般低于VDD/2,而(b)中M17的gate voltage一般高于VDD/2,如果应用中输出的DC bias要低于VDD/2,从减小systematic mismatch角度来看就选用(a)了。

3. 主运放的Noise我感觉都一样,贡献noise的管子是Diff-pair,和M17,M18,M11,M12.输入对管的gm做大,电流镜的gm做小可以减小noise.

4.从电路设计来说,overdrive voltage,sizing, threshold voltage会影响offset,减小DC offset就把增益做大咯,从这两个电路结构来说,我看不出offset有什么区别。至于paper上说CMRR=offset的变化/CM电压变化相关,参看Razavi书上13.2.3

顶一个,大家来讨论吧

discus

这个电路好常见,我觉得除了psrr都是一样的啊!

其中一种结构SR有问题,你发现了没?

我感觉第一个结构和第二个结构在高频的不同可能说的是M13漏端的那个极点,第二种结构由于PMOS的尺寸做得比较大极点会比第一种的更靠近原点。小弟新手,请各位大神指教……

标记一下,回头好好看看

你说的很好,关于你说的我做一点补充,

1,你说的关于M14 source端往上看的阻抗,在低频时候是你所写的,但是我们考虑这个阻抗应该考虑信号频率过了第一个极点时候的阻抗,这时候也就是1/gm14了。所以说我们只关心1/gm14.高频特性PSRR是不是按照第一楼说的A>B,我想还有镜像极点的频率吧,显然同样电流同样vdsat,N mos mirror有着更小的寄生cap。

2,offset的话,我觉得1楼说的有些问题,A与B offset相当,均是与input pair有更大的关系,至于Nmos mirror 与Pmos mirror的mismatch也是有关系,但是两者相当,不是主要的原因。

3,为了减小的noise,将输入管gm做大,current mirror gm做小,两者相差不大。

4,两者的slew 过程,是不同的。SR分为对电容的充电和放电。这是大信号的情况,但是在设计及仿真验证时候,要主要对于A和B 中 cascode管子的 由于大信号使得管子关断而需要一个长时间的恢复时间,恢复到正常工作点后,系统工作状态由大信号的Slew转为小信号的Settling。

顶顶顶

谁把我的坟挖了。

两者的slew 过程,是不同的