有关高速latch及cml的设计

时间:10-02

整理:3721RD

点击:

我最近想设计一个CDR,PD的latch我打算用CML。请问大家的CML LATCH 不管(data&clk input)是开启还是闭关都是在saturation region吗?还是闭关时让他cut off呢?

我使用40nm的制程及vdd 0.9,想要一个可以处理20Gbs的latch, 我试过让 (data & clock)input swing (以及output)为0.9~0.6,也试过0.4或0.5,可是还是遇到有些问题。

VT 大约都是 0.4~0.45左右

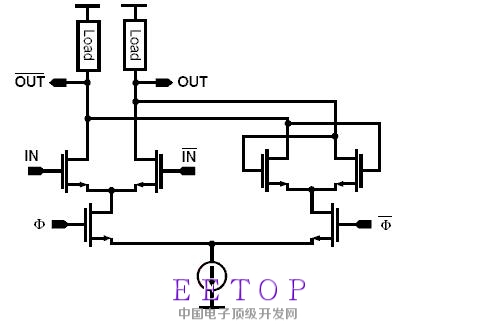

使用的架构是传统的电阻架构

1. 请问大家DATA 和 clock 的input swing会一样吗?

2. 我跑模拟时,我的current source 为500u,R =1k, 我让clk 为0.4时,mos为cutoff,可是mos会有到50u左右的漏电流,使得输出结果或者说function不太对,有什么建议吗?

3.有没有什么其他建议的高速架构呢?(主要是高速+低电耗)

4. CML的input跟output swing是否要一样? (要接成D flip flop再接Phase detector(PD) )

找了些资料,感觉上CML的设计方式蛮灵活的,希望可以讨论讨论。

DING~

ding~