cadence里如何编写理想DAC的veriloga代码

我写的veriloga代码如下,请高手分析哪里出了问题,谢谢!

`include "constants.vams"

`include "disciplines.vams"

module dac_12bit_diff_ideal (vd11, vd10, vd9, vd8, vd7, vd6, vd5, vd4, vd3, vd2, vd1, vd0, vout1, vout2);

electrical vd11, vd10, vd9, vd8, vd7, vd6, vd5, vd4, vd3, vd2, vd1, vd0, vout1, vout2;

parameter real vref= 1 from [0:inf);

parameter real trise = 0.0;

parameter real tfall = 10.0e-12;

parameter real tdel= 10.0e-12;

parameter real vtrans= 2.5;

analog begin

out_scaled = 0;

out_scaled = out_scaled + ((V(vd11) > vtrans) ? 2048 : 0);

省略……

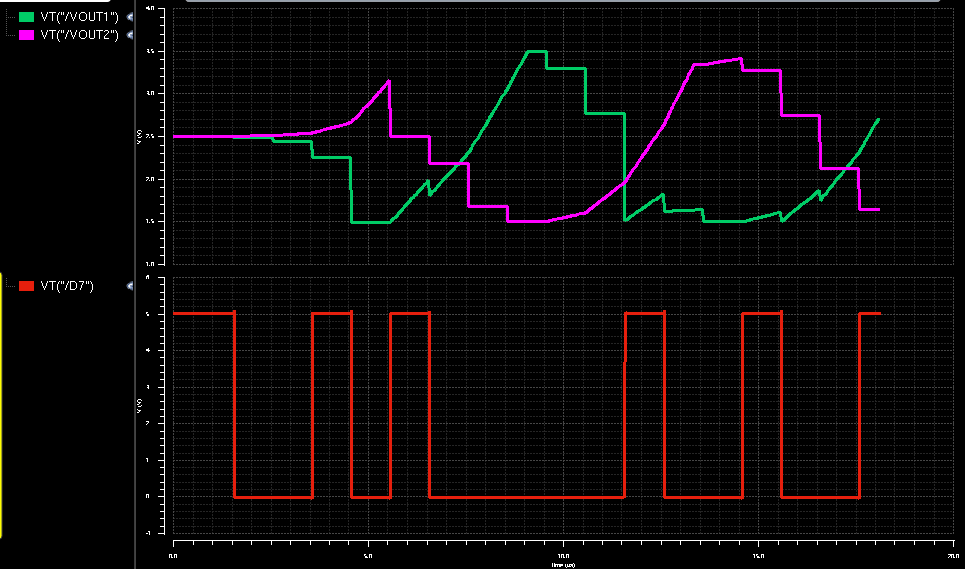

V(vout1) <+ transition( vref*(2.5+(out_scaled-2048)/2048), tdel, trise, tfall );

V(vout2) <+ transition( vref*(2.5-(out_scaled-2048)/2048), tdel, trise, tfall );

end

endmodule

EXAMPLES FIND DA

module ideal_dac(in,out);

input [0:dac_size-1] in;

output out;

voltage in,out;

parameter real dac_size = 2 from (1:inf);

parameter vth = 2.5;

parameter real trise = 0 from [0:inf);

parameter real tfall = 0 from [0:inf);

real code;

integer pow2 [0:dac_size];

analog

begin

@(initial_step)

for (i=0;i<=dac_size;i=i+1) pow2[i] = pow(2,i);

code = 0;

for (i=0;i<dac_size;i=i+1)

code = code + (V(in[i]) > vth) ? pow2[i] : 0;

V(out) <+ transition(code/pow2[dac_size],0,trise,tfall);

end

endmodule

parameter real vref= 1 from [0:inf);

=> 這是要訂?

VREF 可調 full scale range ?

谢谢

这个语法我也不懂,另有一个sample是这么写的

二楼的代码for (i=0;i<=dac_size;i=i+1) pow2[i] = pow(2,i);这个最后pow(2,i)是什么?我看不懂

还有那个dac的话那个输入in不应该是二进制1和0的组合吗?为什么要设置成电路节点的形式呢?code = code + (V(in[i]) > vth) ? pow2[i] : 0;这个in【i】应该不是1就是0,不会比vref大啊,我刚接触veriloga求指导

pow(x,y)表示x的y次方

EXAMPLE是报错的程序为什么呀?

二楼的程序有人验证过吗?为什么总是报错那?

Verilog A is garbage, please use pure Verilog with real variable

小编写完veriloga生成symbol后如何设置的CDF?仿真的时候不报错:Unable to descend into any of the views defined in the view list, 'spectre cmos_sch cmos.sch schematic veriloga……么?

谢谢!

我的VerilogA生成symbol之后就可以直接用,没有设计CDF,你的代码都通过了吗?

如方便,把代码发给我帮你看看。

小编,你好,我最近也在学习verilog编写一个代码用来测试DAC的INL与DNL,

我想请教一下,怎么将verilog导入生成一个可以用来电路仿真symble,我用的是

IC5141 spectre;可以介绍一下你的方法吗?

12345

sorry ..

2Fexample verilogA code have bug

学习一下