pss+pnoise仿真方法

时间:10-02

整理:3721RD

点击:

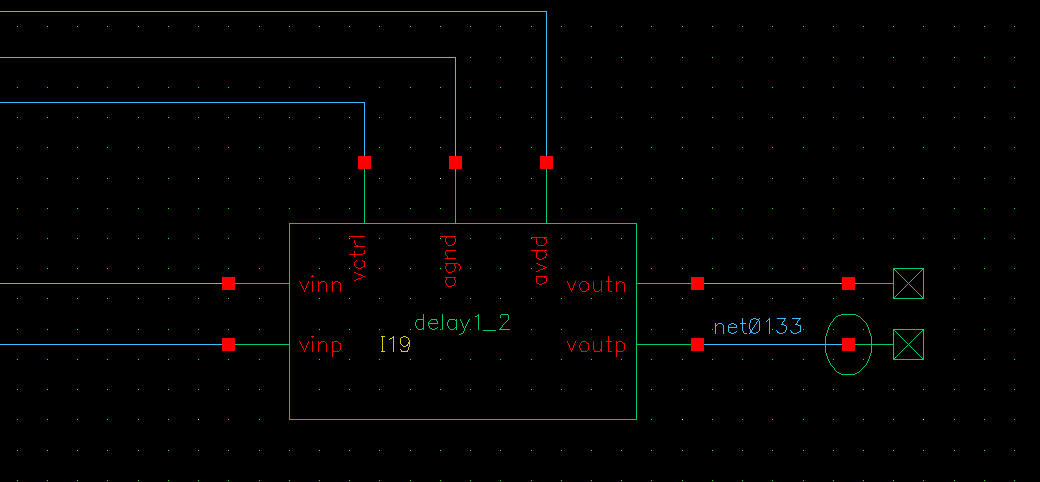

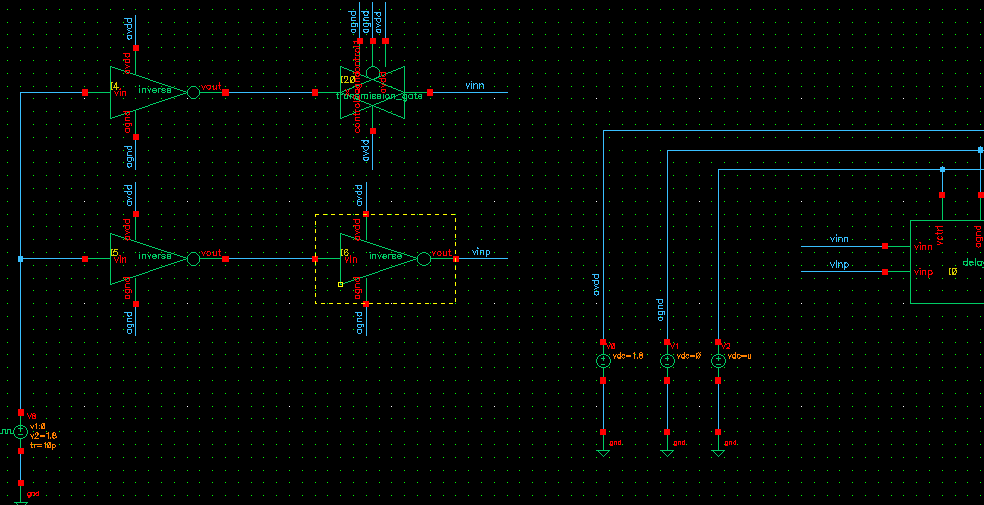

我现在在做一个关于延迟锁相环的jitter仿真测试,但是对于原理图该怎么设置port,以及pss和pnoise怎么设置不是很明白,希望某位大侠可以慷慨解囊。cadence的帮助文档我也看了,论坛里的帖子页看了不少,但是还是不太明白

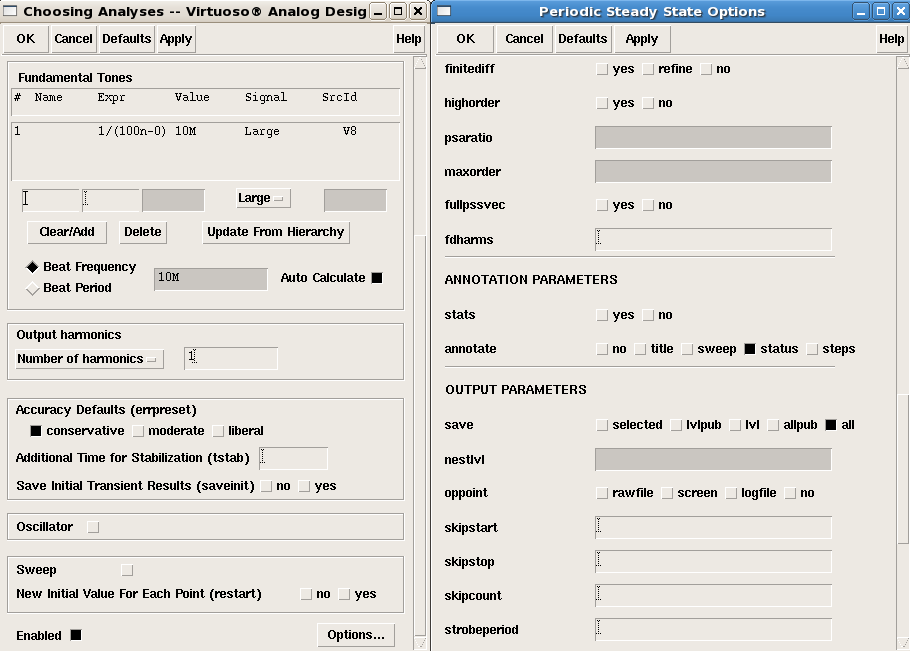

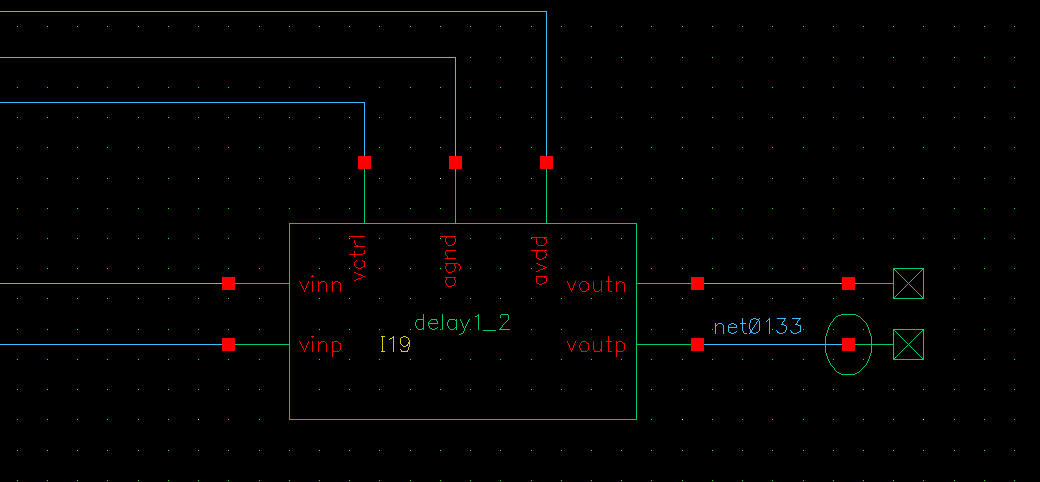

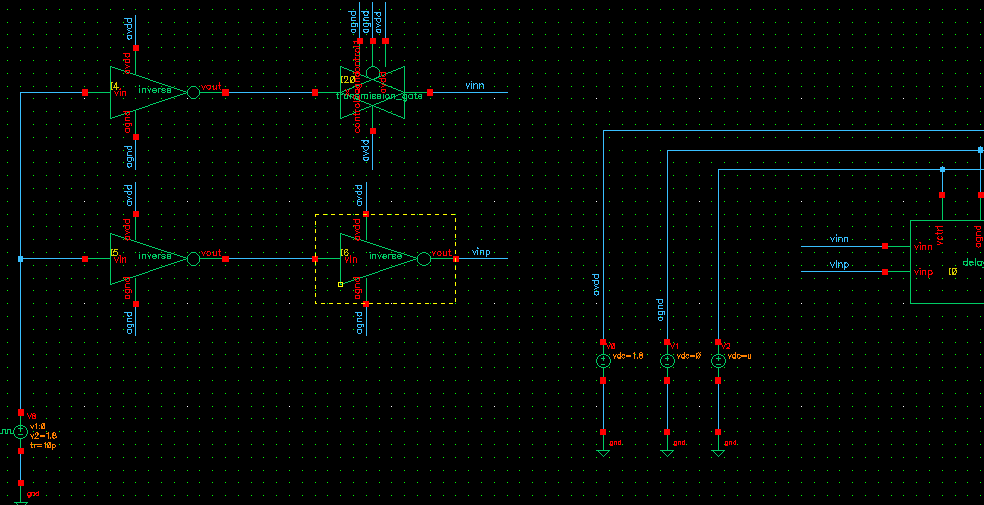

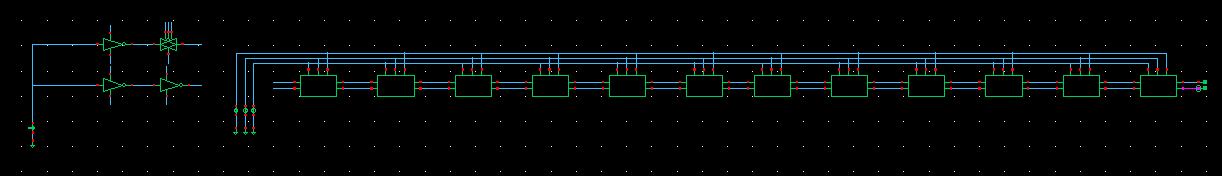

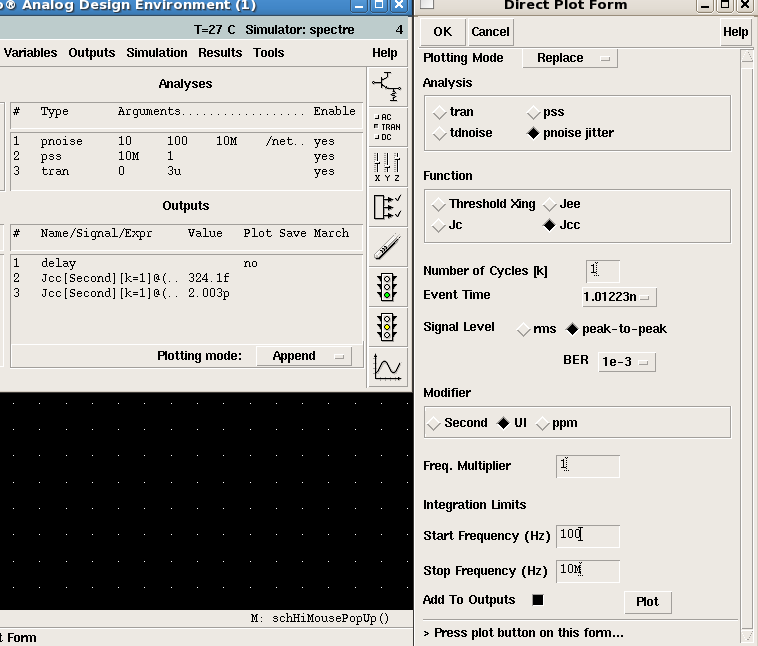

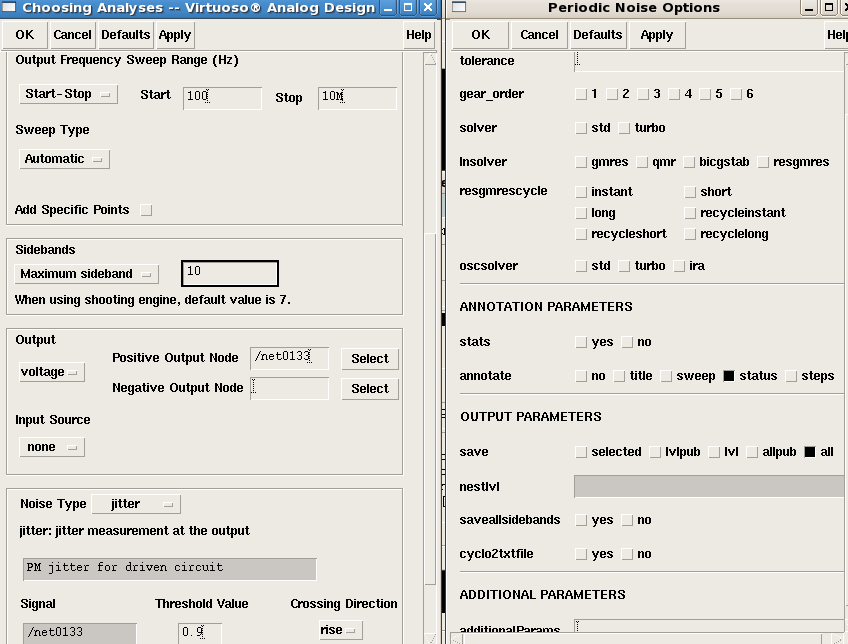

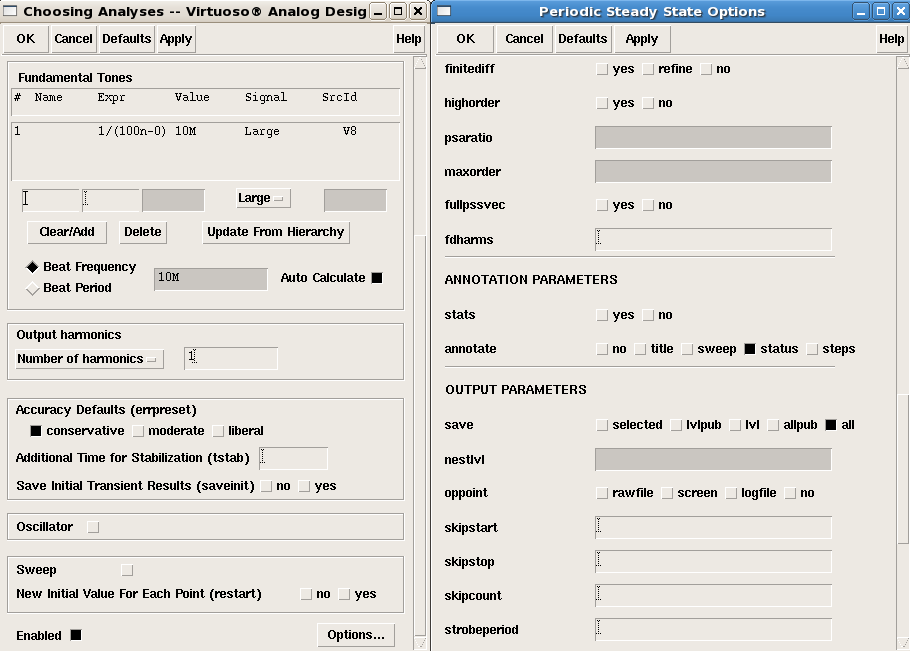

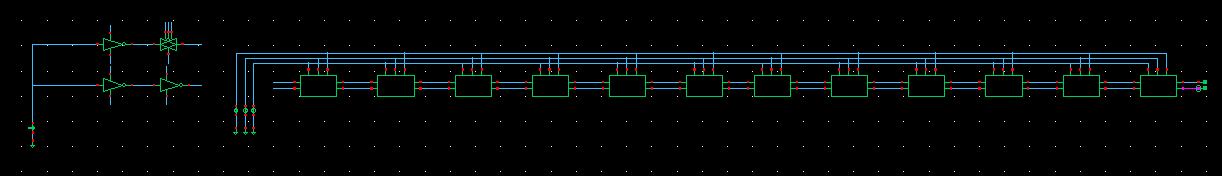

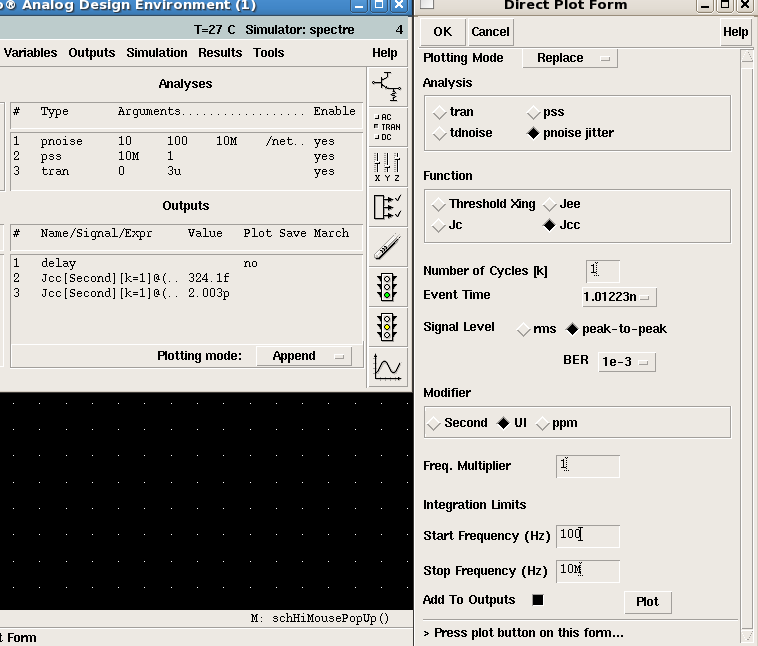

我的原理图和pss以及pnoise的仿真在上面,希望指出我的错误

结果在ADE的仿真器下面

你可以先自己试试,然后具体问

你好,先谢谢你的回复,刚接触jitter的pss+pnoise的方针,希望可以得到你的指点

我的原理图和pss以及pnoise的仿真在上面,希望指出我的错误

结果在ADE的仿真器下面

延迟单元的仿真

pss中sideband设置高点,否则pnoise中sideband再高也分析不到

pnoise里tstab可以设置一下,帮助收敛(通过tran仿真确定电路进入稳态的时间)

pnoise jitter里的k与ber根据应用进行设置

谢谢

1.pnoise仿真是不是模仿器件本身的噪声的?

2.我电路图上有什么明显错误吗?

3.我得到rms和票p2pjitter有意义吗?

4.对于你说的两个sideband我不是很理解

5.对于仿真plljitter,是不是应该先把各个模块的相噪曲线仿出来,乘以相噪传递函数,噪声能量想加积分得到jitter?这个过程是不是必须用到建模的方法?

,请教

fgfdgfdgfdghfgdfg

我也是,,学学

PSS仿真

帮顶!同是DLL这块,请问你最后实现DLL的抖动仿真测试了吗?

有用,学习了。

learning !

小鹿同学!

期待大神的解答。