vdsat问题

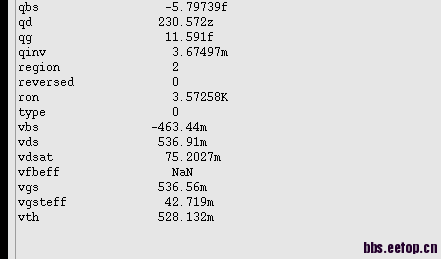

vdsat=75.2mVvgs=536.56mVvth=528.132mV

我大概查了下vdsat不等于vgs-vth的原因

在长沟道下,vdsat=vgs-vth=vod

在短沟道下,由于二阶效应,vdsat就不等于vgs-vth,但这个值,spice

也好,spectre也好,都是用来判断管子工作区间的。一般来说vdsat<50mV

管子基本就工作在线性区。在短沟道下,vdsat几乎不可用手算。另外vdsat

不是越大越好,比如差分输入对,由于要保证一定的增益和带宽,或者是低

功耗设计,vdsat很难做到200mv,一般也就100mv多一些。而且输入差分对

vdsat小一些,对噪声也有好处。反过来,如果是电流镜,工作在深度饱

和区才是有利的

但是region应该是仿真提供的管子工作在哪个区的吧。2应该是指饱和区,3应该指截止区,1是指线性区,不知道我这个有没有弄错。

我想问下vdsat 在0.13工艺下 取多少合适还有就是我的vgs-vth那么小是不是很危险还有在0.13工艺下vgs-vth取值多少合适

的确是太小了,已经亚阈了。vgs-vth取多少取决于是什么管子,如果按你说的差分对的话,100-200mv都是比较不错的值。你的vgs-vth只有10几毫伏,所以仿真器得到的vdsat为3倍的thermal voltage左右

0是截止区,1是线性区,2是饱和,3是亚阈值,4是击穿

0是截止区,1是线性区,2是饱和,3是亚阈值,4是击穿

请问一下关于这些vgs-vth还有vdsat的留的值一般以什么为标准有没有可参考的书籍

还有就是在设计中一般对管子的W L应该都有一定的取值根据你的经验的话对于这些的取值我如何去把握

我之前没设计过

如果是current mirror 当有不错的电压欲度的话, vdsat在typical case取300mv左右,基本可以保证可以pass其它所有corner,同时也取得比较小的mismatch;

如果是differential pair,典型值100mv左右了;

cascode管子(cg device)通常100mv左右吧

帮顶,希望能者回答

单靠一个vdsat怎么就能判断工作区了呢

可用 Allen & Hollberg 的书

学习了

Vdsat =100mV ~ 150mV保險

plot the curve gm vs vdsata, gds vs vdsat, etc. then you know how.

想请教一下,电压余量应该分两个吧,一个是Vdsat(或者说是Vov=Vgs-Vth),控制源漏电流Id;一个是Vds-Vdsat,控制MOS管处于线性区还是非线性区。

在上头讨论的,差分管100-200mV是Vdsat还是Vds-Vdsat呢

另外,“一般来说vdsat<50mV基本就工作在线性区。”这句话应该有误把。应该是Vds-Vdsat<50mV基本就工作在线性区。管子工作在线性区还是饱和区由Vds决定。Vdsat(Vov)<50mV应该是亚阈区。

不知道我这样理解对不对

呵呵 学习了

推推 學習

>=100mV

学习了

小编,在小尺寸工艺中,vgs-vth>0且vds-vdsat大于50mv认为管子工作在饱和区,这样是对的吗?如果vdsat很小,但上述条件仍然满足,电路会有什么影响吗?

学习了,学习了

学习学习

vdast 得80mv以上 算上余量100mv+

学习学习

学习了