求教下自举开关的问题,请看图(boostrapped switch)

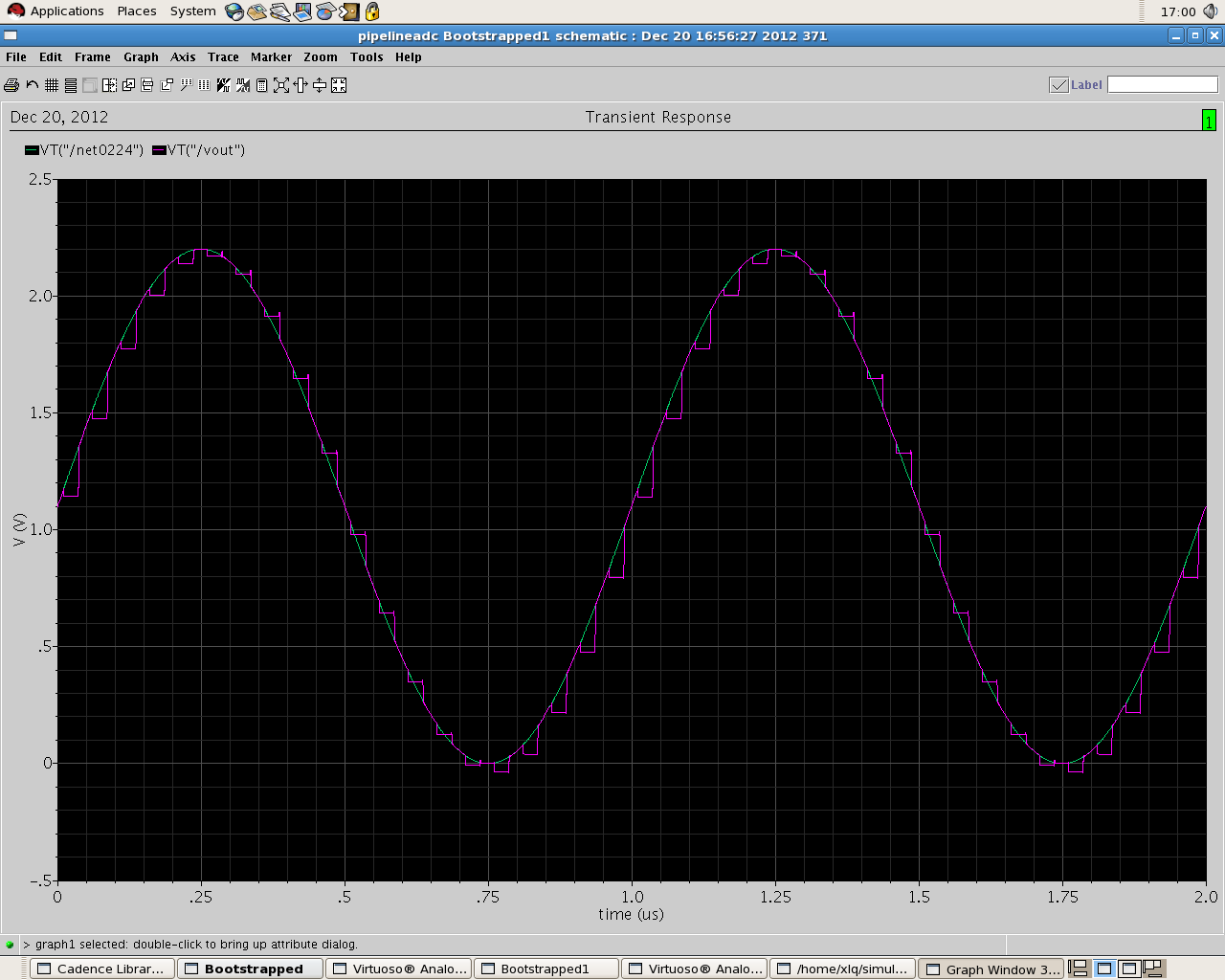

绿色的线是输入信号,红色的是输出信号,当开关处于导通阶段的时候,输出能够很好的跟随输入信号,但是当电路处于电容充电状态,也就是开关不导通的时候,输出电压会先下降,然后才保持不变,分析不出来造成这个问题的原因,有人遇到这个问题吗?

输出信号短接一个1p左右的负载

太菜了没看懂,继续关注中

NMOS开关关断的时候有负电荷注入到电容,另外,时钟馈通也会造成一个误差。

可能是clock透過nmos的Cgd產生clock feedthrough所致.

LZ的SWITCH管子取多大。太大会受charge injection和clock feedthrough的影响,放掉部分电荷。

Vin透過M9後與clock疊加呈現在node n3,這個架構不太會產生signal depedent charge injection!

与输入有关的电荷注入所致,该电荷约为(2*Vi+Vth)*Cgd/(Cl+Cgd). 改变输入,负载电容,管子尺寸看变化。

為何你是 sin wave?

bootstrap一般是 charge pump 電壓到 x2 vdd - Vdiode . ,

都是給方波充電 => 轉移 ,

還是你是想把 sin做 電位提升嗎 ?

還是如果只是想 vin電壓 很高> vdd ,

那先確定 n3點 電位>>vinVOUT .

因為 只有 n3 點比 vinvout 高 vthmos switch 才會 on ,

但有點怪是

switch 是 nmos看圖應該 vin 到 vout間會有寄生 body diode ..

switch 是否該反過來使用 ?

谢谢,呵呵。

首先,谢谢回复的各位~

这个问题主要是由电荷注入等引起的,在我把输入管子调小后,确实得到改善,但是当管子变小,相应的导通电阻也就变大了,电路的动态特性变差,因此我采用了差分电路的方法来减小电荷注入引起的电压偏差

首先,谢谢回复的各位。

我把管子改下后确实电荷注入减小很多,但是这样的话导通电阻变大,动态特性变差了,因此我使用差分的形式来消除电荷注入的影响

是输入信号 不是时钟信号

sin wave是输入信号,为了降低switch nmos的导通电阻,所以用bootstrap把switch nmos的导通电压泵高一点

另外,请哪位老兄解释一下这个电路吧

偶的思维模式很不适合chargepump这类电路

继续关注中

做一个差分的会好一些 ,但是由于开关肯定会存在一些非线性,尤其在高速和低电压下,需要测试一些动态指标以满足设计需求。

赞一个

小编可否说下怎么仿真啊?

老师布置看自举开关,看了些论文,不是狠详细,不知如何入手