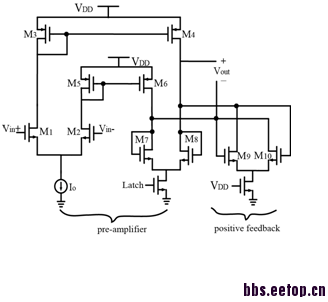

一个简单的latched comparator电路图,大牛指导啊

对于这个电路的工作原理,我这样认为的,当latch高电平时,由于diode-connected mos管的加入,是的comparator的整体增益变大,出现输出的高电平,latch低电平时,comparator只是一个普通的amplifier,增益较小,输出较低电平,不知对不对啊,latch是有什么控制呢,大牛指导啊

对于这个电路的工作原理,我这样认为的,当latch高电平时,由于diode-connected mos管的加入,是的comparator的整体增益变大,出现输出的高电平,latch低电平时,comparator只是一个普通的amplifier,增益较小,输出较低电平,不知对不对啊,latch是有什么控制呢,大牛指导啊

顶一个,大牛啊

Latch为低的时候,就会关死一边的直流通路,正反馈就把原来0到diode电压拉到0-vdd之间,输出的摆幅就增大了,正常比较时Latch为高,可以理解为把负反馈也加入进来,降低增益,不然输出节点就被正反馈一直拉住动不了了。

我也觉得diode通后,output摆幅反而是被钳住了。

还是不太懂啊,latch是由什么控制呢,所谓比较器,reference在哪里啊,可以说的再具体一点吗

顶一个

顶一个啊

这是一个动态比较器,latch就是时钟信号,只有当时钟为高电平时,比较器才比较。看下allen的书吧,比较器那章有类似结构;比较器的基准就接两个输入端的任意一个就行了呀。

不过你的电路是不是没有加复位结构?如果没有复位结构那这个比较器就会产生迟滞的效果。

您说的很对,这表现为一个迟滞比较器,您说的复位结构是指得什么啊?我好好看看allen那章节,貌似有讲,谢谢了

标记一下,感谢各高手

看管子比例,未必有迟滞的

抑或参考jacob baker的书

这个图的出处请告知一下好么~

这是一个动态比较器,latch就是时钟信号,只有当时钟为高电平时,比较器才比较。看下allen的书吧,比较器那章有类似结构;比较器的基准就接两个输入端的任意一个就行了呀。

mark一下。

学习了……

学习了

看到了说下我的观点,不对之处请指正...实质和楼上的差不多...

假设input比较接近在一开始的一段时间还可以用小信号的思路分析,positive feedback那部分可以理解为两个common source amplifier首尾相连,组成了一个2个CS amp的chain,每个都有一个负的,绝对值大于1的gain.这样负负得正,这个chain就是一个pos feedback.这个pos feedback在latch信号为low(0)的时候工作,作用是将pre-amp出来的信号迅速放大,使output一边拉到Vdd一边拉到0.

当latch信号为high(Vdd)时,中间那一路的两个diode-connected的transistor导通,把这个diode-connected的transistor加入到前面的CS amp中考虑,amp的gain现在小于了1,于是这个loop stable了.这种情况下(latch为high)电路又可以“读取”pre amp的结果到output node上,等待latch为low后,重复之前的pos feedback进行放大..

这个电路没有reset好像...

若有错误,请指正..这个电路之前没见过..