锁相环不能锁定的问题,希望有经验的大佬解释一下,不胜感激!

时间:10-02

整理:3721RD

点击:

如图是我的电路图和出来的波形图,我是用十分频电路来做一个输出频率为1G的时钟,结果得到的频率就只有300M到350M之间波动,分频器输出的波形和参考频率差别太大,请问这是什么原因,有什么解决办法?

如图是我的电路图和出来的波形图,我是用十分频电路来做一个输出频率为1G的时钟,结果得到的频率就只有300M到350M之间波动,分频器输出的波形和参考频率差别太大,请问这是什么原因,有什么解决办法?

vctrl波形怎么样?单独仿真反馈分频器看看

目测分频器有问题,检查下分频器,首先保证分频器和每个sub block 都没有问题, 再来跑pll top 仿真。

不好意思,前几天考试没有来看帖子,还是有一个问题希望你们帮忙解答一下。大三刚开始做这些,希望不吝赐教!

分频器我之前做了测试,没什么很大的问题,但是可能由于分频器的输入电容太大了导致vco和分频器连接后原来vco输出的接近方波的变成了类似正弦波,而分频器对正弦波貌似识别得不是很好,所以可能导致这种结果。不知道你有什么办法可以解决vco输出和分频器级联的电容影响问题(之前尝试过源跟随器,结果高频速度跟不上。后来用了反相器,还勉强)。

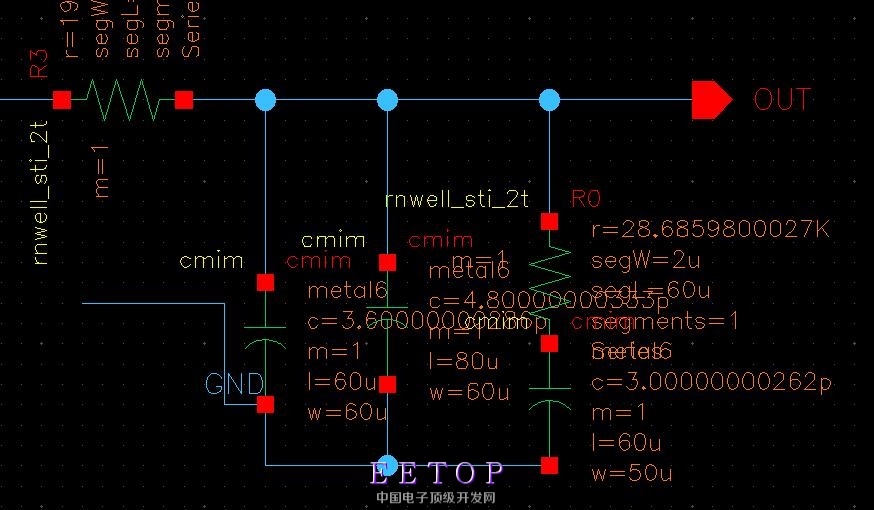

另外还有一个问题,看到其他帖子上说环路增益带宽也会影响,可能是CP电荷泵的滤波器会影响电路工作带宽,但是到底怎么影响的不是很清楚。我们目前做的是一个200M步长的锁相环,输出频率200M到2G。下面是我的环路滤波器,你们看看,还望多帮一下我,不胜感激

不好意思,前几天考试没有来看帖子,还是有一个问题希望你们帮忙解答一下。大三刚开始做这些,希望不吝赐教!我的问题在上面这一楼,希望您能解答!

有没有哪位懂这个的帮我解释一下,正在学习阶段,希望得到你们的帮助!

是不是你vco的输出没整形好。你vco输出如果不接divider,输出是方波吗