请教---请大家评价一下Delta-Sigma ADC的性能

1. 一个(DT) Delta-Sigma ADC 粗糙的目标SPEC如下:

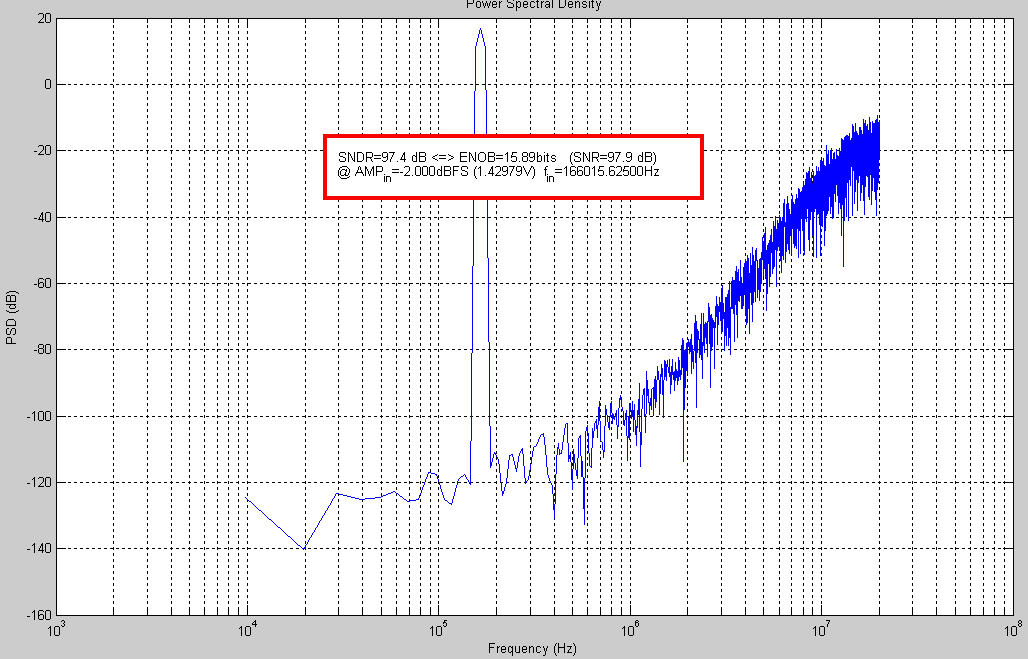

a. 带宽1.25MHz; b. SNDR=92dB; c. 功耗(模拟部分)=28mW (包括OTA+比较器功耗,不包含外部提供的小偏置电流和参考电压功耗). @TT FF SS FS SF corner, -40~+85摄氏度。

2. 不知道上述ADC的性能如何?是不是太落后了?有没有搞头?真诚希望大家指点指点。谢谢!

discrete time or continuous time ?

DT的

0.34pJ/conv. seems ok.

你是要发文章?电路上的创新比较重要吧,specs上ok就行

1. 电路结构跟通常的有点不一样,电路设计快接近尾声了(理论推导有几百页,仿真大概也有上百次吧,仿真结果与理论推导的结果基本吻合)。2. 真实OTA(TSMC .18的工艺,全用normal的MOSFET)+积分系数误差*+电容单元失配误差*+DWA+比较器输入失调电压*(*:表示电路级仿真时人为加入以模拟实际情况的误差),电路的仿真结果如下:

Looks nice !

3-order multibit-q , 不知道noise factor怎么样

功耗不小啊!

请问,您加的比较器失调电压是多大呢?

DWA, 是多bit量化器的?

既然多bit, osr可以降一点,功耗应该还可以优化一下。

7#-10#一并回复:

1. 电路噪声总输出功率:2.4728*10^(-10) V^2;

2. 宽带+高精度的功耗都比较大,但比stanford的 “A low-voltage low-power sigma-delta modulator for broadband analog-to-digital conversion”的44mW低不少。

3. 人为追加的比较器失调电压为-25mV,+25mV,-25mV,...,+25mV,依次交替,每个量化器共8个比较器。

(单独仿真比较器的输入失调电压, 全落在区间[-25.3,+25.3]mV区间内@3000次mento carlo,T=-40~85度)

4. OSR=16, 全面影响各种噪声(泄漏噪声,失配噪声,电路噪声),不可以再降低了。

你好 我现在做一个两位量化的 sigma delta ADC在计算他SNR的时候是不是要两位输出码流 接到一个2bit理想DAC上 然后将理想DAC的输出码流 导入到MATLAB 计算吗?亟待回复 谢谢

just learning !

请问用的是什么工艺?

delta sigma AD的FOM值是咋算的?还请指教。

抱歉想问一个笨问题,

比较器输入失调电压对sigma-delta的影响不是很小吗?

为什么要仿真比较器输入失调电压呢?