关于PLL总体相位噪声的水平

然后仿的电荷泵与鉴频鉴相器的输出噪声

分频器的噪声忽略了

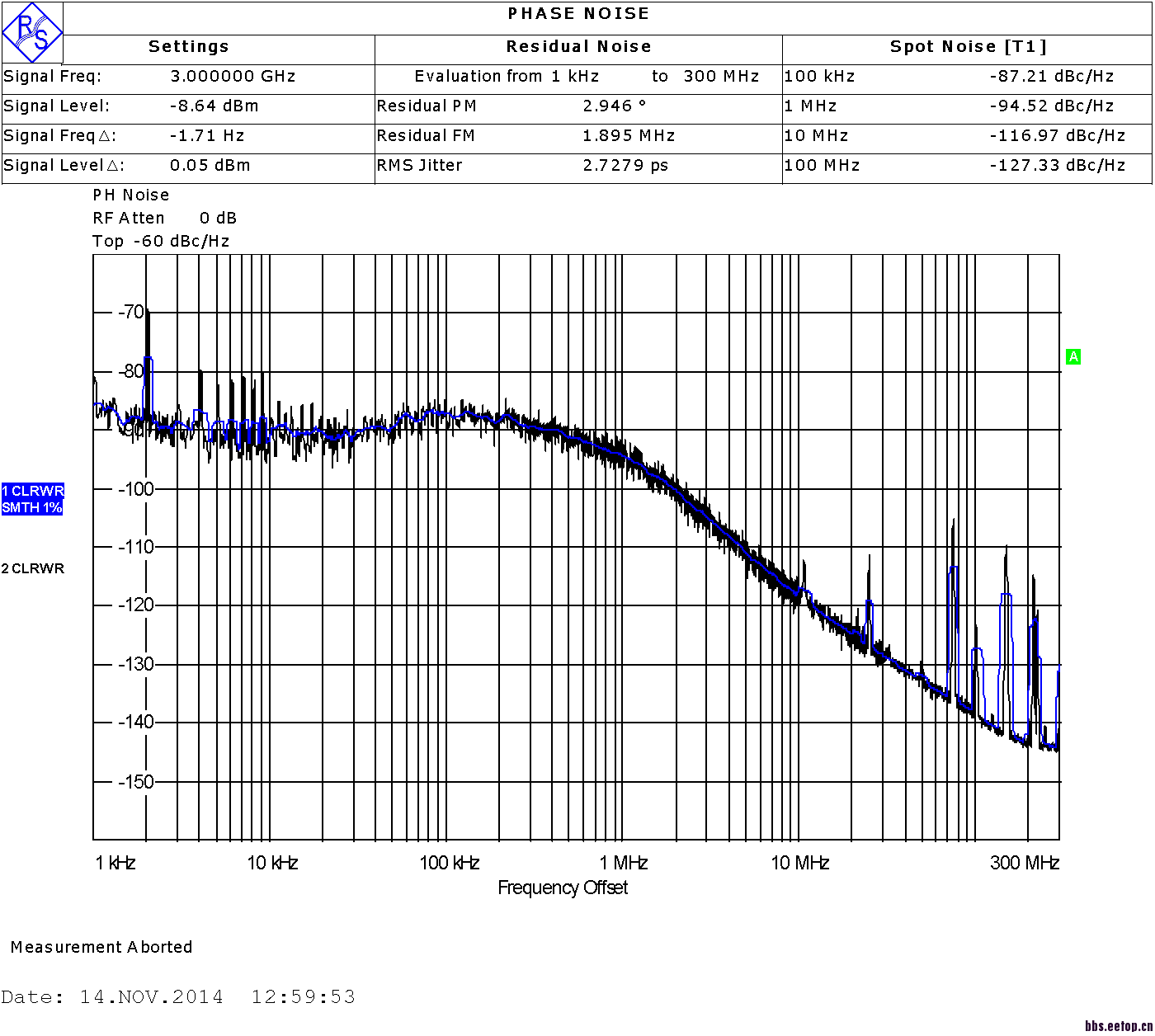

最后用matlab根据传输函数算出了总噪声,居然得到了这么个图。

问一下各位大神,这个图异常么。我觉得总的相位噪声不可能这么低

谢谢诸位

估计MATLAB程序都有问题,VCO的相位噪声贡献曲线明显有问题,还有你的LPF,div的噪声最好也算上,很显然上面没有,PFD+CP噪声贡献曲线也有问题,高频段怎么可能会有一个上升再下降的趋势呢?还有输出单位是dbc不是db,先理解了环路噪声传输函数之后再来拟合曲线吧

好的 我再去学习一下不过dB和dBc在数值上没有太大区别吧多谢了 这么晚回帖帮助人

还有鉴频鉴相器 电荷泵和LPF是一起仿的Pnoise

phase noise当然有可能在bandwidth附近会有一点突起,那个频率附近vco phase noise最高

楼上的意思是PFD+CP对于总噪声的贡献在高频处不应该有突起。但是我仿的时候是PFD+CP+LPF一起仿的,出来的应该是电压噪声。

我的VCO仿真的相位噪声应该是没问题的

请教一下大神,我的低频相位噪声是不是有点低?是不是因为LPF输出的噪声是电压噪声的原因?LPF噪声的传递函数是不是就是输出的相位噪声对于电压噪声的传递函数?

第一次仿 没有什么经验 见谅

还有我觉得自己所有的模块都没有进行优化,都是用的最传统的结构,我觉得总体的相位噪声不应该只有这么低。

谢谢...

我觉得你先把传输函数搞清楚,整个pll loop的开环、闭环传输函数,各部分传输函数写出来,包括vco, charge pump, lpf, pfd等

如果phase margin不够,那么close loop是会在bandwidth附近有突起,pfd和cp的noise就会凸起来

至于phase noise的高低,这和vco频率,ref频率,分频系数等都有关系

只要model和测试结果match就可以了

cadence仿真的phase noise还是很准确的,至少我实测和仿真结果非常吻合

总的输出相位噪声在环路带宽肯定是会有一个突起的,这个突起是由LPF处的噪声和VCO处的噪声贡献带来的,但上面我说的是PFD+CP的噪声贡献,这个噪声贡献在环路带宽之后是以20dB每十倍频速度下降的,只要稳定性足够,这个环路带宽处一定平稳下降,除非当你相位裕度严重不足过度欠阻尼的时候,这个地方才会有一个抖动峰值,那是不希望看到的结果

你VCO自由振荡的相位噪声可能没什么问题,但你这个图中VCO的噪声贡献曲线是一定有问题的,VCO噪声传输函数为高通滤波器,低频段的噪声贡献曲线一定是严重下降之后再慢慢上升一直到环路带宽处后再慢慢下降,看你这个VCO噪声贡献曲线,应该是你把VCO噪声传输函数搞错了

首先,你是PFD+CP+LPF一起仿真,所以你的曲线中间凸起是合理的,因为电阻的噪声在滤波器后是带通的。但你VCO噪声是有问题的,因为低频的VCO噪声会被抑制。最后,总输出噪声中间凸起也是合理的,凸起不凸起取决于design和VCO的类型。但我想知道你VCO和参考时钟频率是多少?100dBc/Hz @1MHz还是很不错的。有没有考虑电源或者Regulator的噪声?

还真的是,VCO的噪声是高通特性吧?那应该就是我搞错了 我去看看我的传输函数。谢谢啊。

只考虑了VCO、CP、PFD、LPF、以及一部分的输入参考噪声没有考虑电源噪声和分频器的噪声

所以噪声可能偏低

输入时钟10M 输出160M带宽1M 还是比较low的参数==

你好!你是怎么用cadence仿真PLL噪声的,如果可以给我一些资料看看,感谢了啊!

给你个网址,自己去看

http://www.ece.utah.edu/~ccharles/ee536/

请问实测的时候input reference 以及power/IO引入的Noise带来的影响大吗?仿真的时候怎么模拟?

你好,我是一个matlab小白,请问一下看输出相位噪声,软件中有自带的模块,还是需要自己写程序呢?谢谢