一个输出1.8V的LDO ,电路中所有管子选0.18um工艺中的1.8V管子可以吗

如果你能保证各种上电、掉电、正常工作的情况下,所有管子都没有耐压的风险就ok啊。片外电容的吗?那这样还要考虑下LDO输出管的ESD问题。

选什么关子和你的输出关系不大,关键是你的电源电压是多少。

您應該選IO Device to design your LDO.

对,我看0.18um工艺库时,3.3V的管子是3.3V IO nmos,而1.8V管子是1.8V core nmos;那个IO与core,是什么,他们有什么区别?

典型VDD=3.3V 转1.8V,

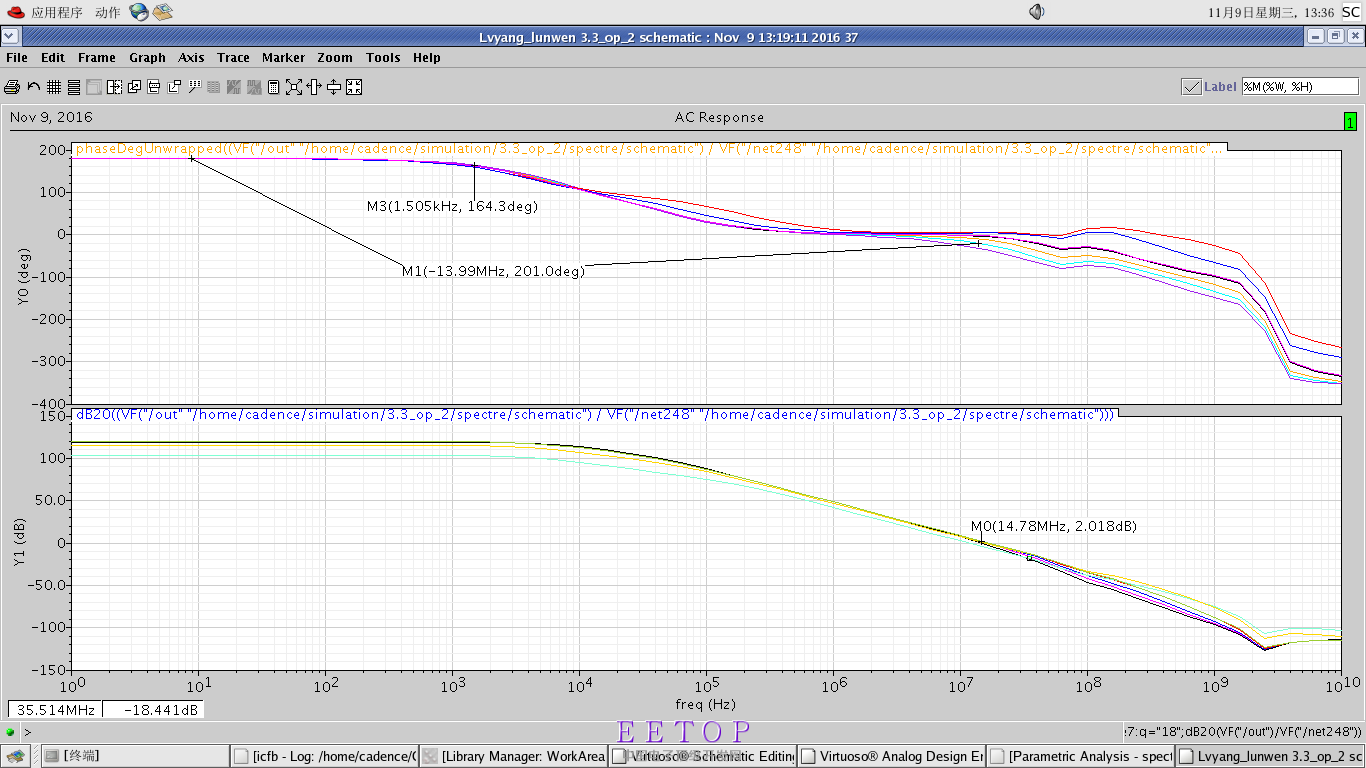

capless LDO ,,,管子选择的问题,已经解决,典型vdd=3.3v,转1.8V,那还是得选3.3V的管子,那么有个问题不解,我的论文LDO结构为一级折叠放大器+buffer+功率管,为无片外大电容,一般下级负载电容为10p以下,分析时,文献说,1.8V输出时,若负载电流从0.1m-100m变化时,等效电阻在18-18K变化,那么输出端最低的极点位置近似等于1/18k*10p=5.55M,也就是说LDO输出极点在大于5.55M的频率以上变化,次极点为LDO输出端,在高频变化,主极点为第一级折叠放大器输出端,而buffer输出端也在高频范围;那个相位仿真图,是没有任何补偿时仿真的,参数分析法,负载电阻从18/180/1.8k/5k/10k/18k变化,所以,我这个主极点,次极点,是怎么分布的,有点弄不懂了,

那你只能用vdd=3.3的。本身器件应用电压就是根据vdd来的。你可以看一下pcm文档里不同器件的bkvds的电压, 在3.3v vdd下器件会击穿的。

嗯嗯,明白了,关于选管子问题已经解决,而且,我的这个LDO,所选结构为,一级折叠+buff+调整管;主次极点也你弄明白了,但是buff用的是最简单的P管跟随器,此跟随器输出阻抗中等,此时buff和调整管产生的极点,不高(频率),得换成低输出阻抗的,让buff和调整管产生的极点处于更高频,能否推荐个结构,

有个超级跟随器的,其工作电流随负载电流变化,可以尝试

这种情况下,选型3.3V的肯定最好,不过也是看需求,USB接口的芯片进来的电压都是5V,5V转3.3V的LDO都是3.3V 的IO MOS做的。1.8V相对3.3V的管子一个是速度快,一个是面积小,当然耐压值要小很多。

LDO的主、次极点随着loading的变化也是在变的,这个是正常的。只要能补偿到各个工作点都是稳定的就OK了。

请问你们工艺有pps电容吗

kankankan看看怎样

不错不错