two-stage opamp slew rate 模擬的疑問

时间:10-02

整理:3721RD

点击:

大家好

小弟目前對 two-stage opamp 進行 slew rate 模擬時,遇到了無法理解的問題。

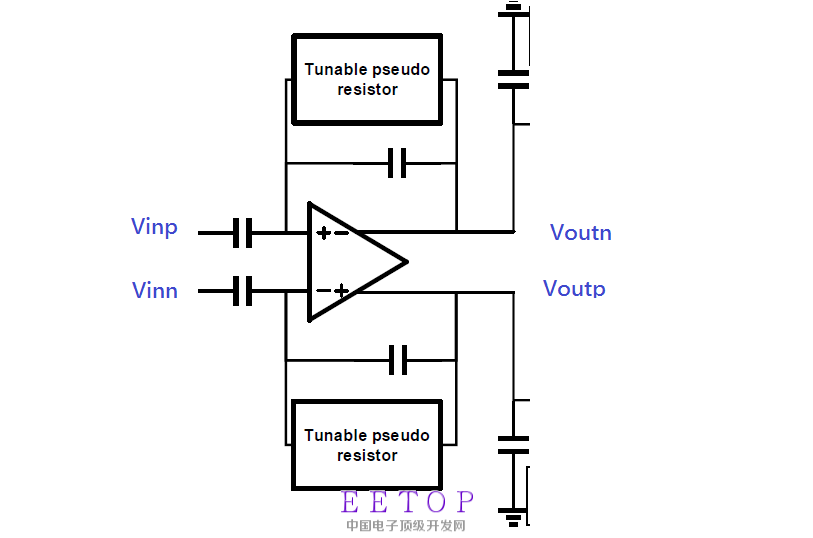

電路 schematic 如以下附圖:

這邊定義 Vin= Vinp - Vinn,Vout= Voutp - Voutn

模擬方式,我是在 Vin 端灌入理想方波。

這裡我有一個疑問,給的方波是要從 0V ~ VDD,還是從 -VDD ~ +VDD ?

1.如果 input 為 0V ~ VDD ~ 0V (Vinp= VDD/2 ~ VDD ~ VDD/2 ; Vinn= VDD/2 ~ 0V ~ VDD/2)

我預期的 Vout 結果應該也會接近 Vin,

然而實際模擬結果卻有些奇怪,Vout 有隨著 Vin 從 0V 拉高到 VDD,但是當 Vin 從 VDD 降回 0V 時,Vout 卻不是停在 0V,而是 -VDD。

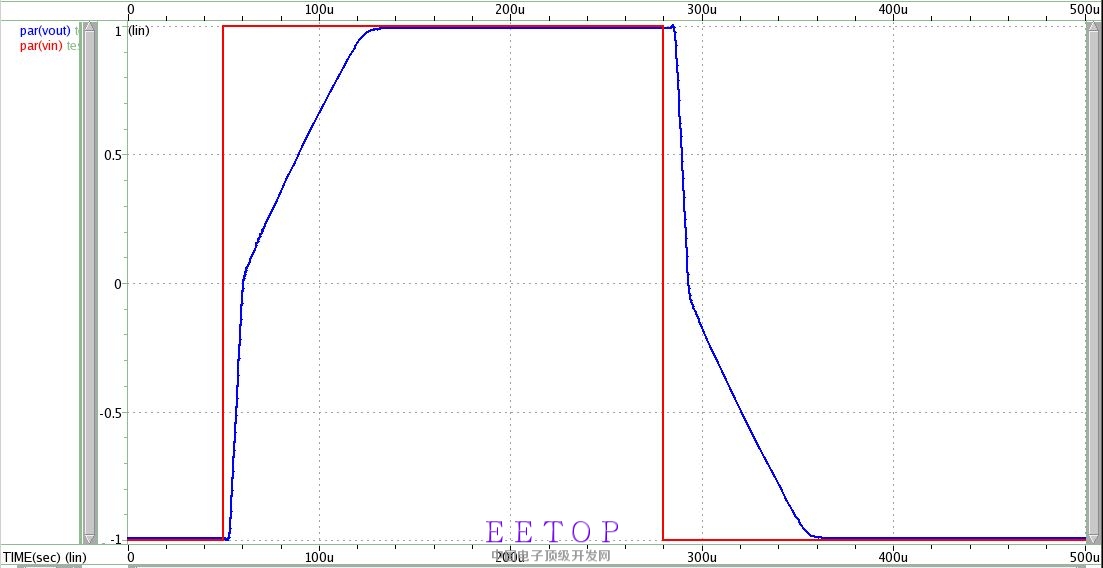

如下圖所呈現 (紅線為 Vin,藍線為 Vout)這部分感覺有些奇怪。

2.如果把 Vin 的方波設定為 -VDD ~ VDD,則 Vout 也會趨近於 -VDD ~ VDD,如下圖。這樣看似合理多了

想請問大家,這樣的 transient response 是合理的嗎? 若是不合理,最有可能的問題是出在哪部分呢?

謝謝大家了

=====================================================================

2017/05/27 更新:

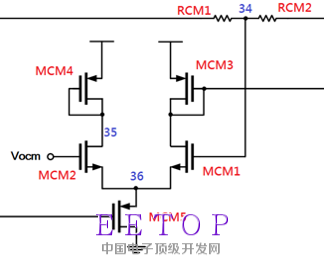

我來更新一下目前發現的情況,首先我是接成負回授的電路,schematic如下圖:

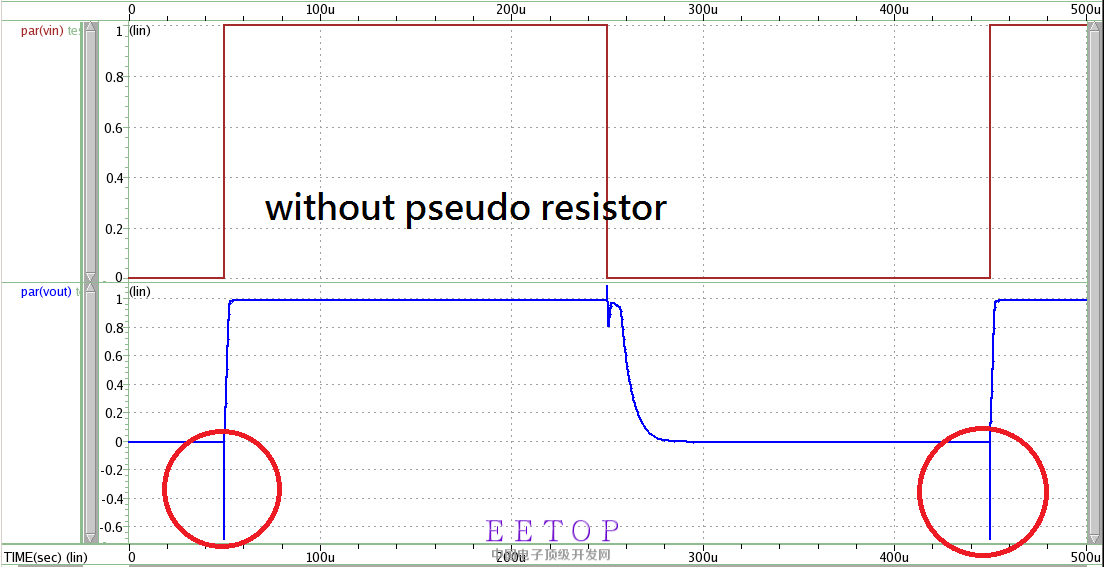

1.我發現 pseudo resistor 或許是造成 slew rate 奇怪現象的主因。當我把 pseudo resistor 拿掉,Vin 給 0到 VDD 的方波,看起來 Vout 也會在 0到 VDD 之間,除了紅圈處有些奇怪,如下圖:

2. 若加上 pseudo resistor,則 Vout 會不明原因被拉到 -VDD,紅圈處也是我無法理解的部分,如下圖:

我正在思考是否因為回授路徑上電容充放電的關係,造成 Vout 會掉到 -VDD 的現象。

====================================================================

2017/05/29 更新:

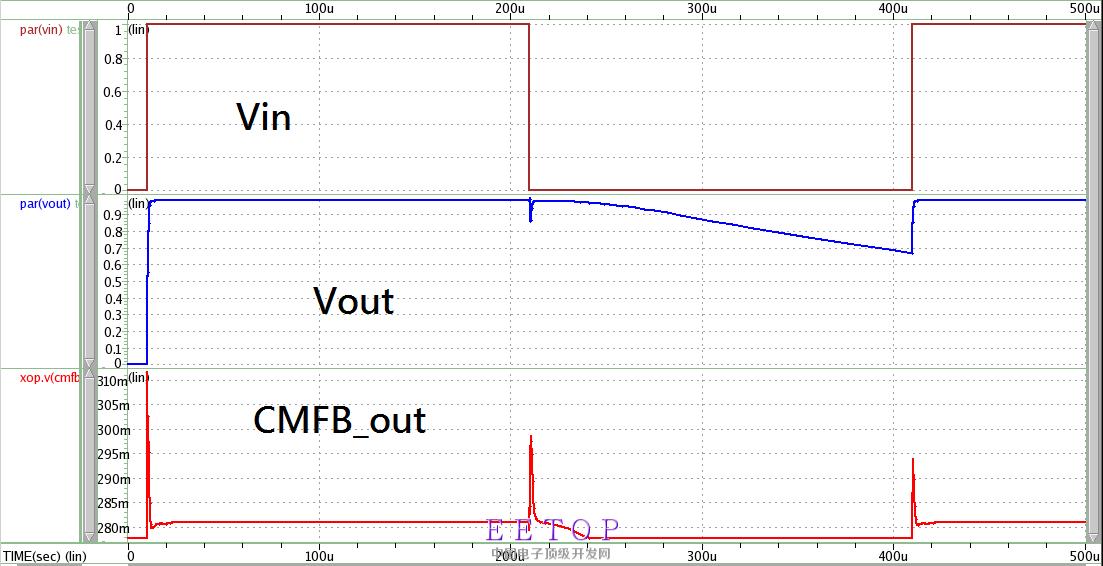

測試 open loop 特性,發現問題應該不是在 feedback 路徑上,因為 opamp 本身的 negative slew 就有問題。

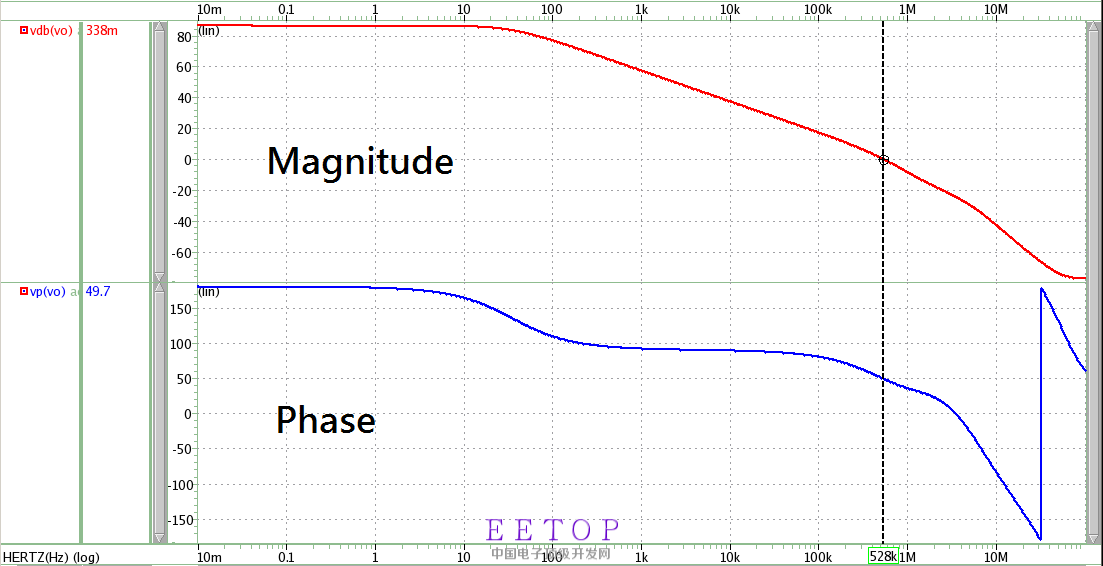

以下是模擬波形圖,問題似乎是出在 CMFB 不穩定?

但是實際測試 CMFB 環路,基本上確定 phase margin 是夠的(如下圖),應該不至於造成 transient failed,想請問大大,最有可能的原因是出自哪呢?

开环or 闭环

共模反馈是怎么做的

是閉環電路,我已更詳細更新目前的發現。

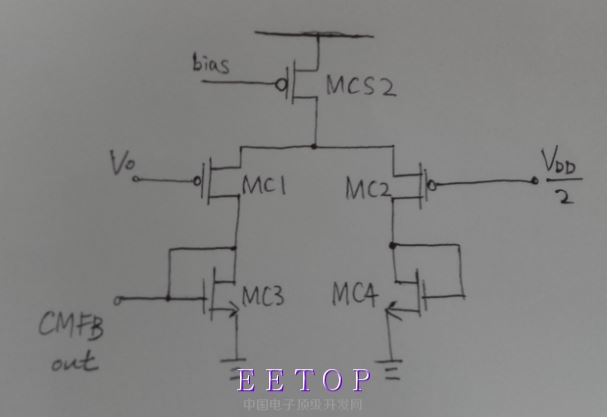

common source with diode connected load 這種架構,只是為了方便設計,我把圖中的 pmos 和 nmos 對調。

目前看來,問題好像是出在 feedback 路徑上 pseudo resistor 與回授電容這部分。

MCM5管是pmos?你的pmos和nmos对调是什么意思?

好的,不好意思。我再畫一張圖並重新編號,如附圖這種接法。

其中 MC3 MC4 為 nmos,其餘為 pmos

你有多跑几个周期试试吗,接上电阻会变成high pass,而且这种电容输入的建立时间一般很长。那个glitch没什么,输入翻转的时候通过电容给输出冲了电 ,放大器建立没那么快。

你好,我實際測試更多的週期後,波形沒什麼變化。目前我懷疑問題是出自 CMFB 這部分,我已更新最新發現,希望您有空能幫小弟指點迷津。萬分感謝!