ESD 求大牛解惑

一小公司的有个产品,是消费类的。比如户外的流行灯 驱动芯片 因为成本压力。只能在die上省省面积来争个一分两分的。margin 很低。由于芯片的通道很多 16个。 ESD 很占面积。

这里有一个问题,关于ESD的。

1. 如果用工艺厂提供的ESD,硕大无比。但又无其他选择。目前用的ESD仍然是他提供的,但是按照耐压估计只有1KV左右。(使用了推荐的一半尺寸,有2kV 降到1KV,风险多大啊?),不知道这个有么有问题?

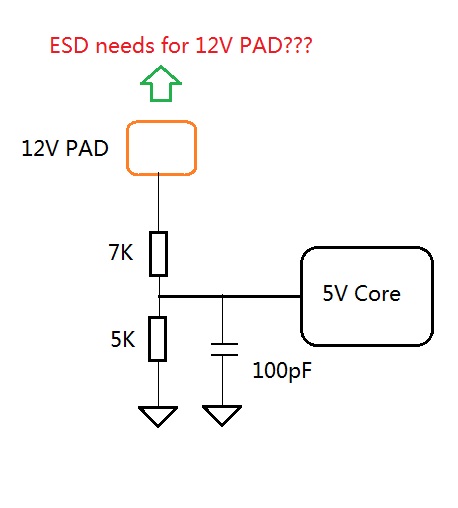

2. 关于其中的一个ESD,是 12V的,通过内部电阻分压(7k+5K)+200PF的电容滤波给 5V给内部数字供电,那么这个 12V的power PIN 需要单独的ESD么? 风险如何。

3. 我们是这样的,如果客户使用中坏了芯片,我们直接给人家换一颗芯片。但是如果fail的太多了。很是很糟糕哦的事情。

我是做电路的,ESD经验较少,这里请各位有经验的大牛不吝赐教。

工艺厂提供的ESD是啥器件,尺寸多大啊?比如几百um的ggNMOS?

你们芯片的电源地是怎么给的,是通过芯片周围的IO环还是直接PAD输入?

另外1kV对于你们产品的良率会不会有影响? 对于这样的低价封装可能封装环境对ESD的要求不能太低,2kV靠谱点。

另外12V电源那个还是要给ESD防护器件比较好。

消费类2KV是必须的,1KV太不靠谱。

什么工艺的?

就是帮朋友做个产品,如果到了2KV,ldmos的 需要5000u/0.6u ,layout 整个面积到了1W um^2 16个通道太大了

再恢复一下补充:

工艺厂提供的ESD是啥器件,尺寸多大啊?比如几百um的ggNMOS?

A: 是nldmos 高压12V的,》2KV 需要 5000u/0.6u 巨大,因为通道多 15个要用,所以。

你们芯片的电源地是怎么给的,是通过芯片周围的IO环还是直接PAD输入?

A: 地是有地的PIN,然后底线绕芯片一圈。

另外1kV对于你们产品的良率会不会有影响? 对于这样的低价封装可能封装环境对ESD的要求不能太低,2kV靠谱点。

没与专门的ESD用,2kV要是做了,该芯片没有任何盈利。

另外12V电源那个还是要给ESD防护器件比较好

A: 12V的可以不要么? 已经有RC滤波了啊。或者仅仅在5V哦那边加5V的 ESD?(其余的都是Ldnmos)

如果5V电源引脚上有ESD保护单元,那么12V的电源引脚可以省掉ESD保护;厂家提供的器件经过了验证,并不一定是用一半面积就只有一半的ESD保护能力,当然,单独的保护单元可以抗住HBM 2kV的冲击,并不代表能够保护内部电路在2k ESD冲击下不损伤。12V的驱动输出采用LDMOS器件的话,有的结构可以自己保护的。建议还是用代工厂的结构,在进行试验流片时自己做点面积小的单元进行积累。ESD保护对工艺的依赖性很大,一般来讲相同的结构更换工艺时仍然需要进行优化。

LED电流输出的工作电压和ESD都是12V的对吧?量了一下聚积的一个18V输出16通道的LED,ESD面积32um×140um^2

损坏的芯片有做EMI分析确定是ESD的原因吗,是EN SDI SDO等引脚还是16路电流输出引脚ESD损坏啊?

1.這個由12V分壓給5V的電路 你們應該用LDO (with large external Cap or without large external Cap) 而不是用電組這個請你們RD改 可以用(LDO without large external Cap)

2.只有出pin的PAD才要加ESD (只要出PIN都要加)

3.不同power domain ESD path也是要用diode string 串起來 (不然PIN to PIN ESD test 你就過不了)

4.你可以參考substrate trigger 技巧滿不錯的 (我沒有說可以抄喔! 我也沒建議你用喔! 只能看一看而以喔! 照抄是犯法的 要用合法的方式 你自己斟酌研究) 但是那是TSMC的pattern, GGNMOS是滿大的

5.如果覺得ESD不夠大可以加大ESD電阻 不然你也可以用兩級式結構

HBM的测试模式是150pf,2kV通过1.5k的电阻向PAD放电,在不加12V ESD的情况下,2kV/(7k+1.5k)=200mA的电流,也就是200mA的电流要流过这个电阻啊

谢谢朱先生的指导。对我以后的工作很有裨益的。

另外我还有一问? 该12V的ESD仅仅有电路分压再进入内部5V core,如果ESD坏了。最先是坏在哪里? 电阻被烧? 还是内部5V 期间被打坏?

您太客氣了 ESD電流路徑很難預測 不同ESD測項有不一樣的路徑 跟電路還有layout 元件結構有很大關係 你的電阻建議是用NWELL電阻 因為那對地就是一個NP Diode 可以傳導掉負ESD pulse (PN forward bias)與正ESD (reverse PN breakdown) 我也只上過課 懂一些皮毛 之後我會努力研究 再跟大家分享

高压pad好像确实不需要更多的ESD保护了,因为高压管子自己都有很好的保护。

对不对啊?

实乃老师之楷模,后生敬佩

这么说也对也不对,高压LDMOS确实有esd的功效,但也面临不均匀导通的问题,因为power管面积很大不是所有的finger都能同时导通,导致只有部分支路能泄放电流,又由于snapback特性栅上的电压被拉到较低电位,致使其他支路永远也导通不了。有时候也需要给power管做单独的esd保护,scr的会常见点吧

高压管子钳位电压高,例如5V钳位,流过1.3A的电流,换成高压10V钳位,也流过1.3A的电流,这个功耗大了一倍

我认为如果12V那个pad只是接了电阻没有接其他电路,不需要加ESD保护。第一,电阻是不会被ESD损坏的,电阻不会有break down电压,ESD电荷会在PAD上集聚并缓慢通过res泄放。

第二,这么大的串联电阻,对后级电路的保护是足够的,发生ESD时大多数能量都被电阻吸收了,如果不放心,可以根据具体情况在后级加小尺寸的次级ESD保护电路。

个人理解。仅供参考。

学习学习

markmark

学习了

12V的PIN自己也需要一个ESD

如果我没记错的话,对于芯片内有二级电源的esd的做法是供电电源和二级电源之间需要一个esd管。另外1kvesd的话风险太比较大,很容易出问题。

HVESD 要小心

大牛牛,谢谢