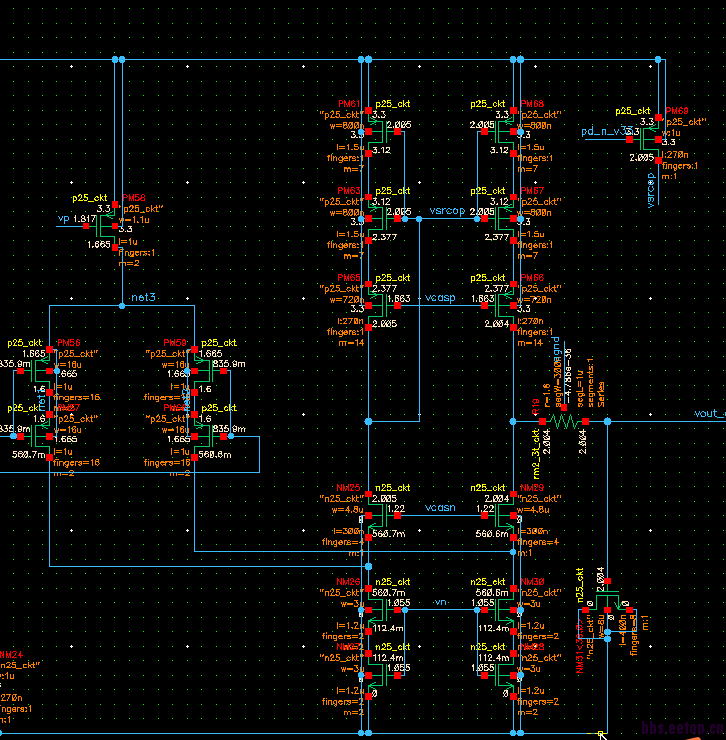

带隙基准电压中的运放设计

这个运放中有三处地方都用到了这种NMOS管串联,PMOS串联的结构呢,好像叫什么Self-cascode structure,请问这样接的好处是什么?我看那个差分输入管用的PMOS管串联,这样反而减小等效跨导,对噪声和失调都不利,那为什么还要这么接呢?求高人指导

这样就是把L增大了两倍吧,还有啥目的呢?坐等高手回答

low power?

谢谢你的回复,增大两倍的长度为什么不直接用一个长为2倍的PMOS管,而要两个PMOS管串联?

有分析是说在lowpower设计中,节约普通cascode 串联bias的2个管子中的1个,或者是节约1路bias。

我觉得还是有一些其它的好处,比如说在layout尺寸一样的前提下(近似地说,1个w/2l的管子,和2个w/l的管子在尺寸上相当),self cascode稍稍使得输出阻抗变大一点(20%左右)。在你的电路上作负载的P和N这2个currentmirror就是利用了这点。

differential input 上的使用,我不是很确定。由于管子的W/L比原来的W/2L要变大一倍,gm=sqrt(2I*KP*W/L)比原来的sqrt(2I*KP*W/2L)要大上sqrt(2)倍,是不是这个好处?

如果是我 肯定就直接L*2低功耗设计中是应该这样增大晶体管的L,不过看你电路里的尺寸,也不是特别低功耗的应用

也说不准版图匹配上有考虑

跟模型有关系,两个单元管的效果并不是说就能用简单的几何加减就得到相同的作用。

在电路中设计者想按照自己的要求去任意设置管子的几何尺寸,但是实际上并做不到,所以制造工厂会提供一定几何尺寸大小的单元器件和模型供设计者使用,如果设计者想要高出倍数或几分之几的器件,则必须用标准单元管来进行组合。

两个10/10管子串起来和10/20也许差别不大,(尺寸大), 但是两个2/2串起来和2/4一管子的差别可能就比较大,工艺线宽越窄,差别会越大。所以在设计中还是老老实实地用厂商提供的模型的器件进行设计,否则

仿真的结果会和实际的结果会有意想不到的差别。

就是增大L。 因为在小工艺下,比如28nm,L最大2um,如果要再大就这么搞。

对噪声和失调都有益吧。如果L=2 和两个串联,后者offset小写,但占的面积也大。

有时候不用L太大,也是layout 上的考虑。如果你的design L和W都一样,匹配是最好的。

我用的就是28nm工艺的,好像有点理解了,谢谢回复

谢谢您的回复,还有一个问题我不是很理解,就是上面电路图中的输入差分PMOS管,为什么要设置fingers=16,m=2呢,总宽为16u,这样fingers宽为1u,这个时候PMOS长为1u,fingers宽与PMOS长都为1u相等,是不是就是你说的最好的版图匹配呢?

m=2等效为总宽加倍为32u,可不可以直接用一个宽为32u的管子而令m=1,这两种情况有什么不同吗?谢谢

真不错。

poly的最大面积也有限制。

个人理解:

这种self cascode的结构一般用在深亚微米的OP中,用来提高输出阻抗,从而提高增益。

原因:在深亚微米中,L比较小,输出阻抗也比较小,故采用上述结构

版图匹配好一点吧

谢谢分享!

学习学习