bandgap测试结果离散性很大,请各位大神支招

最近流了一款带隙基准,输入10V,输出1.2V电压,P/NMOS采用的是高压MOSFET(没有monte carlo model)。

后仿在各个corner下,输出在1.2V+-30mV范围内;

但是测试结果很不理想,测试了10颗:有一颗1.0V,3颗1.4V,1颗1.35V,其余在10%以内(测试环境:室温);

测试结果离散性很大;请各位大神支招。

1、启动电路是否正常工作,会不会有启动没有脱离的情况。

2、这个结构,PTAT,和CTAT结构的mismatch都会被放大,注定分布不会好。电流镜的匹配需要做得很好,考虑你用的是高压管,为了省面积,你的版图匹配多半是不好。

以上

非常感谢回复。关于1,设计的时候也注意了这点,不过是一个查找的方向;

“PTAT,和CTAT结构的mismatch都会被放大,注定分布不会好”不太明白,能否详细些?

另外关于电流镜除了layout匹配外,在尺寸方面有没有什么建议?

“考虑你用的是高压管,为了省面积,你的版图匹配多半是不好”,什么意思?

两边的电流镜适配都会被电阻比例放大。

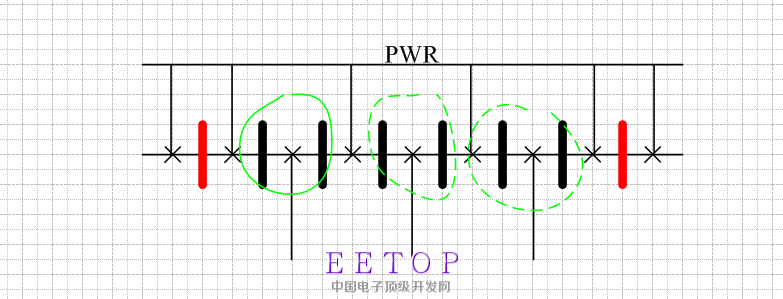

高压管都不能共漏画成finger,匹配会差。可以考虑把PMOS靠近电源的管子都换成低压MOS的话,匹配就好处理很多。

谢谢。

1.今天去查了一下,启动电路不存在“没有脱离”的情况;

2.可以考虑换成中压管的可行性。

3.从公式上看,Vref=R3(VBE/R1+VTln8/R2),参数上R3约等于R1,均约等于10R2,mismatch确实被R比例放大了,但是另外一种结构,Vref=VBE+R3VTln8/R2),PTAT 的mismatch基本也放大了相同的倍数。感觉这两种结构,mismatch的放大效果上相当。(?)

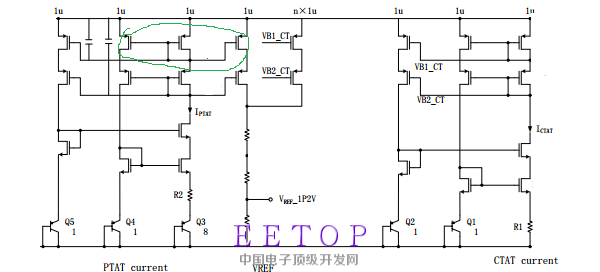

4.PTAT中靠近电源的三对高压p管(1#图示,W/L=2*3u/5u),是这样画的,

高压管画成finger为什么匹配会差?

Hi, 我是KK;

从你的电路架构来看,左边产生IPTAT电流(Vt*lnN)/R2,右边产生CTAT电流(VBE/R1),然后两路电流叠加产生Bandgap电压VBG=((Vt*ln8)/R2+(n*VBE/R1))*Rbg, Rbg为Bandgap输出pin下面串联的电阻;

那silicon的bandgap电压输出偏差很大,肯定是上面公式的实际值超出了typical设计值(在假设你电路设计的typical值没有问题的情况下,这个你可以仿真);

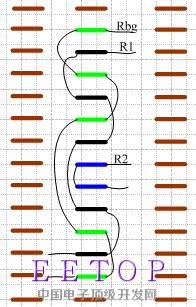

那么,哪些因素会让bandgap偏离实际计算值呢?从公式来一一分解:Vt=kt/q,不取决于你的版图和尺寸;ln8成立的条件为bipolar的画法,如果采用的3*3经典架构,那么肯定是很好的matching,如果你有用share NWELL的方式来画,会造成一定的影响,因为bipolar的beta值会发生变化,但是这个影响不会有这么大,而且这个可能已经在model范围之类了(如果工艺的PDK比较成熟);那么,R2/Rbg呢,这个很大取决于电阻尺寸的选择以及layout的画法,如果用的电阻尺寸太小,以及layout没有使用matching的画法,这个影响会比较大;

再看第二项,n的成立条件取决于PMOS镜像的准确性,同样,不合适的尺寸和layout都会影响到matching,而且你的设计用的是HV MOS,有的HV MOS的mismatch差,就更会影响到电流镜镜像;对于电流镜该怎么设计,简单一句话:L很重要,W不太重要;这里不详述,可参考基础知识的学习;VBE的准确性不会差太多,尤其是VBE本身的bipolar最重要的参数,如果这个model都差很远,那只能说是一个没有节操的工艺了;最后,R1/Rbg的准确性参考以上关于R2/Rbg的论述;

所以,如feel100提到的: 这个电路的bandgap输出电压精度,一个是电流镜的镜像精度(包括1:1, 1:N),尤其是HV MOS, 有没有mismatch的数据可以参考,电路设计是否合理(尺寸选择,layout);

二是电阻的比例,同样与尺寸和layout有关;

最后,个人对design的建议:不是所有电路跑PVT才是worst case,对于高精度电路来说,mismatch更是要义;在缺乏mentocarlo model的情况下,好的designer应该可以自己根据model的参数手算,不要做spice monkey;如果model本身参数缺少,则考研设计者本身的经验以及debug的能力;

非常谢谢KK详细的解释与建议。用的是55nm工艺,foundry没有montecarlomodel,也没找到HVmos mismatch的相关数据作参考,所以一直没有得出直接的数据反映mismatch有多大;

这版电流镜典型尺寸,PMOS W/L=2*3u/5u,NMOS W/L=3u/5u,RES 采用的是2K/方块的电阻,segment L/W =8u/0.5u,感觉电流镜和电阻的尺寸分配的偏小,但是不能得出数据反映 尺寸增大到多少才能使mismatch降低到一定范围内,很困惑;

在版图方面,BJT3*3采用的经典画法,电阻是类似下面进行匹配,电流镜没有做匹配(5#),电流镜版图还需要进一步完善。

从你的回复来看,bipolar和电阻的layout都没有太大问题;当然,55ns选了W=0.5的阻值,应该不会很差;

另外,如果bandgap偏离很多,除了上述的mismatch的原因外,还有可能电路存在某些异常,并且仿真不能验证的,比如NWELL漏电,等等;所以,case by case;

对于这种情况,我建议你选good IC和failure IC 去做probe+FIB对比,可以测测VBE,电流镜出来的电流,然后定位具体是哪个位置出了问题,再进一步分析是matching的原因还是其他类似于漏电,异常的原因;

设计上如果考虑期间的mismatch会更好。如果有从新设计机会。我建议无论 pmos的cascode 还是地下 nmos的都采用 cascode, 高压模型的适配是很严重的,(非对称设计)。我建议 cascode 的管子分别采用 HV PMNOS以及NMOS, 而电流镜采用 5V 的管子 最底下的NMOS 也采用5V NMOS以及HV NMOS cascode保护(别用你一个管子版本,因为10V电压够够的)。 这样既解决了高压问题,匹配也不是问题。 再者电阻我还是建议 采用 W》1u》0.5u 。

谢谢建议。

不知道工业上有没有这样用的:cascode电流镜一个用高压器件一个用低压器件,另外在启动等节点电压跳变比较大的一些状态下,5V管会不会有危险,是个考虑的问题。

今天又了测了一些,大概有70颗了,做了下统计分析,平均值到了1.28V,均方差130mV.

应该不会有漏电,测试没有发现奇怪的电流,分析上没有发现PN正偏或击穿的情况,如果有漏电,结果也应该往一个方向偏,不知理解对不对。

不知道具体是什么工艺。看了一下大概有几点问题。

(1)结构问题,PTAT+CTAT认为增加了CTAT branch,增加了一路mismatch,如果不是对CTAT有要求,完全没有必要这么做。

(2)电阻L=0.5um太小了,以tsmc65nm为例,L最小做到0.4um,但是要做match和控制方块电阻的情况下,没人会用最小的L,一般PDK调出来的defualt L=2um是比较常用的,L=1um也能接受,而且L大一点,W也会大,电阻面积大,对控制电阻比例关系有帮助。

(3)PMOS电流镜size不算大,HV的MOS match会差一些,就像IO MOS比 core device 差一样。 底下的nmos也要考虑mismatch,VTH的offset直接进了ΔVBE,而这个ΔVBE才54mV

(4)通常来说,高压下的bandgap更容易做,有更大的headroom可以利用。要在1V supply下做,会痛苦一点点。

看一看先

用的是55nm工艺,电阻W最小做到0.4um。

你关注的问题没错,正常工作没有问题,要注意上电过程。比如非常快速上电。会担心低压pmos管子问题,在实际应用中会有latch保护。 但由于一般电源上电不会快的离谱的nS级,所以内部上电一般可用。回到小编电路,在我看来至少nmos使用完全没有问题。

CASCODE 电流镜低压在上面,高压在下,高压是开关,只是VDS高压,设计中注意VGS保护,同时注意瞬态。

偏差的主要来源:

1:最上面的PMOS,和bjt上面的NMOS,假设这两个合起来产生5mV的偏差,就会在输出产生50mV的偏差,现在有两个支路,偏差会到70mV;

2:电流镜的偏差,假设2.5%,那么在输出也会产生32mV偏差,结合两路就是45mV;

这样加起来就有115mV了,加上其他的,应该和你实测差不多

建议:所有管子WL同比例加大,那么sigma也能成比例减小。

谢谢。这种cascode电流镜的设计理论上应该是可以的。

目前还没有这方面钳位保护的设计经验。

您能不能再推荐一些资料。万分感激。

像这种高压PMOS/NMOS,工艺上限制W>=3um,L<=10um,原来PMOS尺寸取2*3um/5um,vdsat约200mV,尺寸同步增大的话,如2*6um/10um,再大的话,vdsat就100mV+了,总感觉这么高的电源,MOS vdast取的太小不合适。另外尺寸增大到2*6um/10um,离散程度会减小多少,没有失配参数,只能靠粗粗地估计了。

同比例增长宽长比会减小vdsat?

建议高压P管用isolated P管代替,如果有的话。注意isolated P管的耐压。

同比增大当然不会了,意思是2*6/10是同比增大的最大尺寸了;如果再增大尺寸,只有增大W/L了,这样Vdast就减小了。

这种管子有什么好处吗

PTAT的NMOS vdsat or vod是多少呢? 是幾V的device, 電流是多大呢

相对于常见的高压管,它的match比较好

Vdsat减小些没关系,WL增大,失配能大大减小,要看主要矛盾

isolated NMOS 是不是有五个端?然后让那个多出的端(nwell)悬空来用在高压下吗?最近正在研究这种管子,不知道怎样使用,麻烦介绍一下啊

弄錯方向了, 問題在Q3/Q4 上方的NMOS

通常是高压nwell做ring,和n型埋层一起接高电位构成隔离。建议看它的cross-section。

fab提供蒙特卡洛的模型的话,就跑跑看,是否和实际生产的数据匹配。

如果数据匹配,那就说明mismatch没设计好。

不匹配的话再分析,应该是其他原因造成的。