带隙基准设计时,运放的正、反输入端一直都不能相等(不是失调电压的影响)

时间:10-02

整理:3721RD

点击:

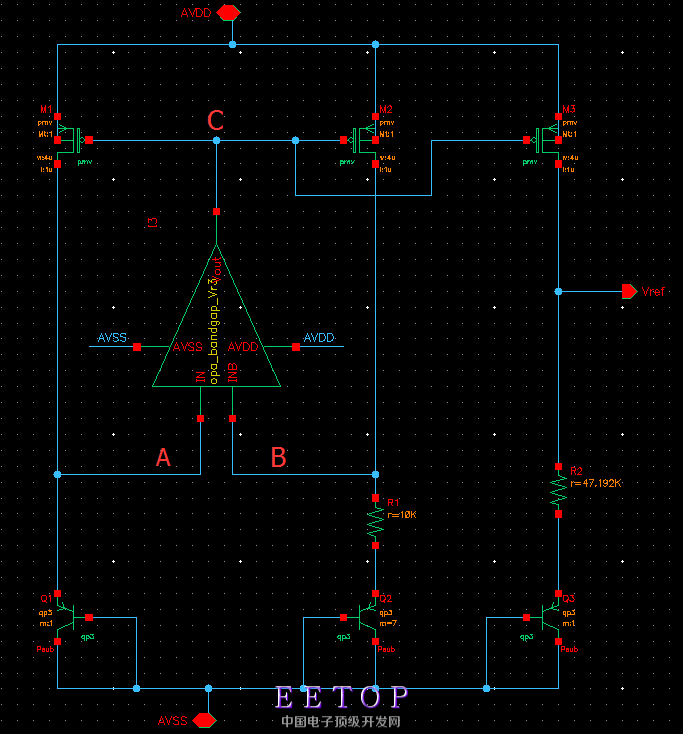

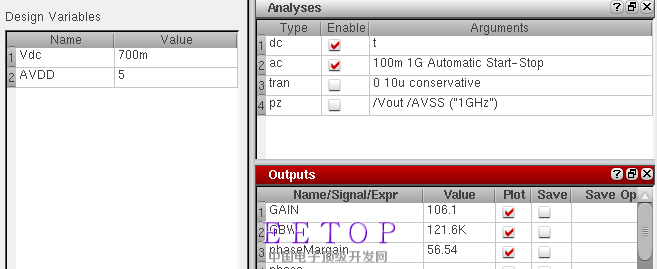

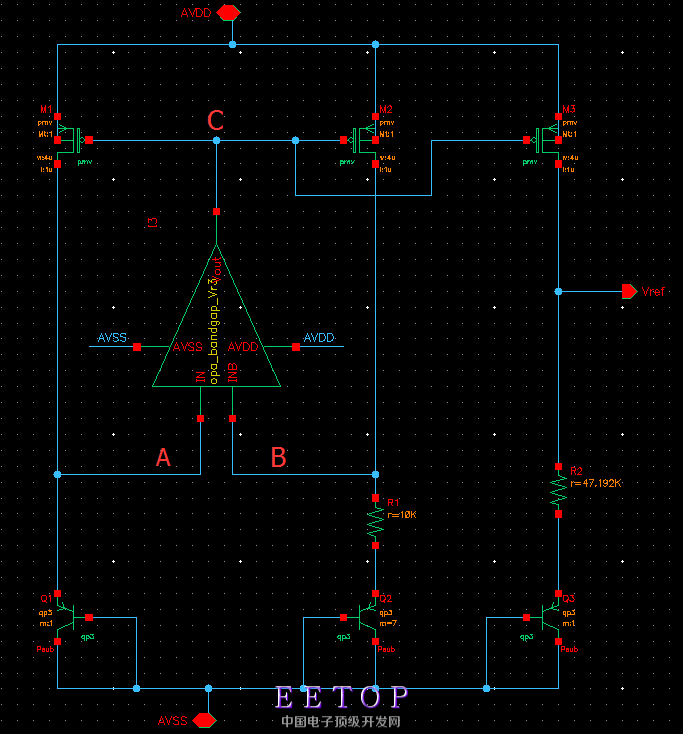

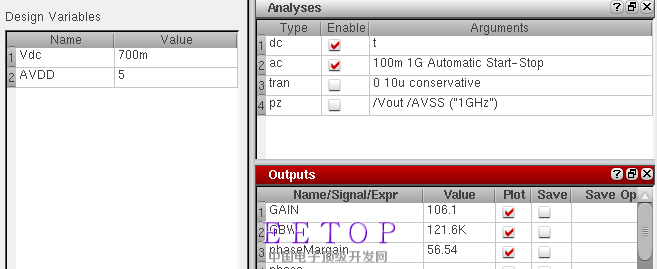

大家好,最近刚学设计bandgap,看了网上的一些资料,准备先调一个简单的bandgap,如下图所示。其中的运放已经调好了,在输入共模电平500mV~2.5V之间(电源电压5V),增益都可以达到100dB以上。带宽很小,只有几百K。在输入共模范围为700mV的时候,其增益和相位裕度、带宽如图2所示。设计好运放后,调bandgap时,我是先仿真出了所用PNP管的V_I曲线,根据PNP管的V_I曲线选择合适的电流,再去计算R1和R2的值。现在的问题是,无论我怎么调节M1、M2的宽长比,运放正、反输入端一直都不能相等,根本没有办法钳位。因此不能进一步调节bandgap。大家在设计的过程中有遇到这样的情况吗?

图1

图2

图1

图2

运放接反了

厉害!现在正常了。用计算出的R1、R2的值,试了一下,温度系数:22.2ppm/℃。再优化一下。但是我想不明白为啥运放的正负端接法会对PTAT型带隙基准有这么大的影响?

Q2较大,因此其Vbe较低。 =>在启动时节点B电平较低(不等于节点A,除非BG正在工作)。 =>连接时,opamp输出停在高电平。

在任何情况下,无论电路是否正确,BG都需要启动帮助(模拟可以始终启动,但不是真正制造的电路)。

书上都有写,仔细看看书,全都搞清楚了,能大概手算了,再去搭电路,仿真一下,看下你算得差多少,得有个方法能大概估计出结果,要不你就靠试取设计了。

这个原因是因为你接成正反馈了

我就是通过手算来调的电路。先仿真Q1、Q2的V_I特性曲线,取一个合适的PTAT电流,看Q1、Q2的Vbe差值,可以算出R1、R2。用工艺库的电阻,各个工艺角的温度系数为6.6-11ppm/℃。做之前我看了何有年的红书,没有看到关于描述运放正负接法对其的影响,所以忽略了这一点。现在明白了。谢谢你!

现在懂了,谢谢你!