在Cadence里面用verilogA编写一个分频器的symbol

时间:10-02

整理:3721RD

点击:

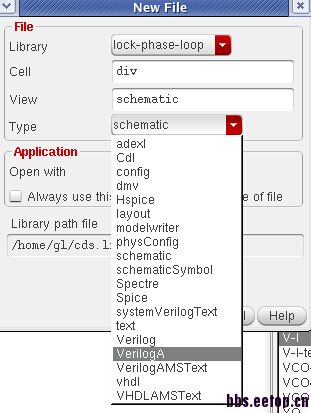

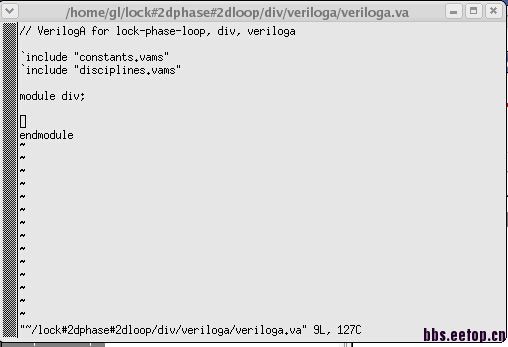

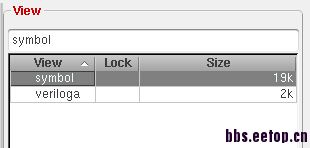

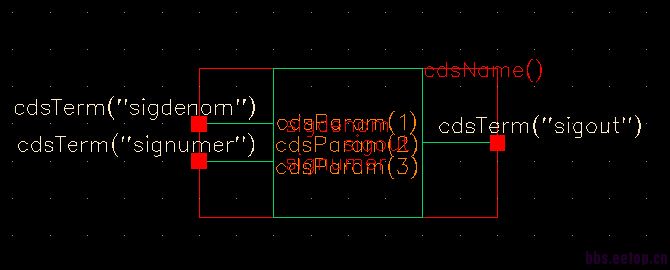

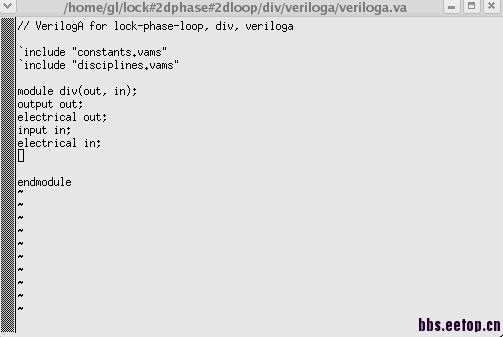

我写了一个用verilogA语言编写的分频器(div)代码,想把它在Cadence中转化为symbol,供我在进行PLL系统级仿真时提供模块,但在Cadence中转化为symbol的操作我不会,求解答,不胜感激。第一二两张图是我会的操作,但不知道怎么样把它做成symbol,就是做成类似第三四两张图的结果

我之前做法是手动建立,自己画一个symbol,添加pin,仿真时会自己匹配,如果和你的代码端口不一致,会报错

个人没找到直接生成的办法,还请大牛告知

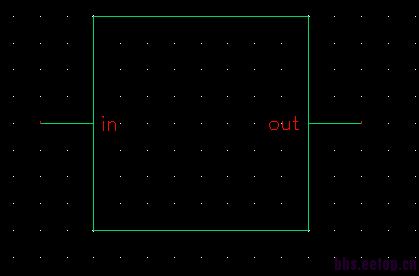

您好,谢谢您的回复,我按照你说的方法自己画了一个symbol,定义了pin in和out,然后又建了verilogA,在代码框输入分频器代码后,但我不知道怎么保存了,每次写完代码,把这个代码框关了之后再打开,代码又消失了,估计是没保存,请问怎么保存的?谢谢第一图是我自己画的symbol,第二图是把verilogA和symbol放在了一起,第三图就是代码框了,准备把代码写进去,但这个代码框上面怎么就没个save之类的保存按钮呢?

作verilog就好了,为啥verilogA?

verilogA的view是verilogA,verilog的view是functional

试试按下esc,然后输入 :wq(冒号是要输入的)

verilog-A好像是的

太感谢你了,终于解决问题了!正确的输出了任何分频后的方波!搞了几天了,总算没有白费!

能否共享一下分频器的代码?

PLL高低频混合仿真,采用行为级应该可以快很多

mark一下,多谢分享

verilog-A 和 verilog 还是有很大区别的啊

支持一下

多谢分享

大恩不言谢。

Create→Cellview→ From cellview