一个用于小数分频的调制器结构

时间:10-02

整理:3721RD

点击:

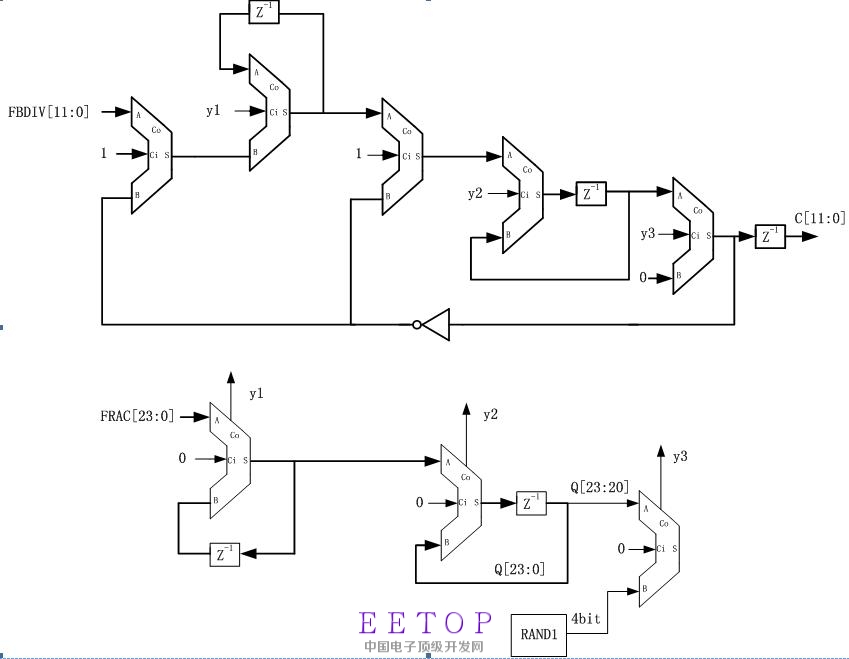

一个用于小数分频的调制器结构如下:

谁能说下这个结构调制器的原理吗?C[11:0]直接送到反馈分频器控制分频比,谢谢!

自己推导

推不来,老师没教过啊,论文上也只有MASH 1-1-1结构的推导。你看这个结构还有反相器,这不按套路出牌啊。你会?有本事推出来给我看看啊。

没人会吗

是一个典型的二阶单环反馈的DS调制器结构,输出应该不用12bit,这里有误

输出就是12位,只不过就低三位在跳

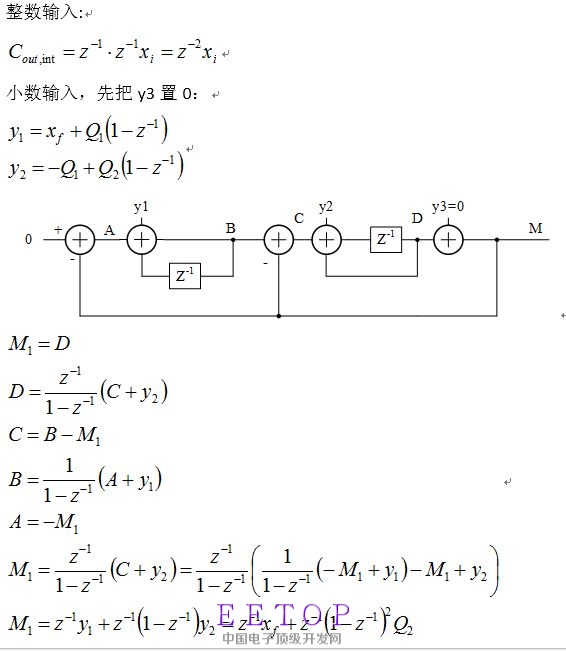

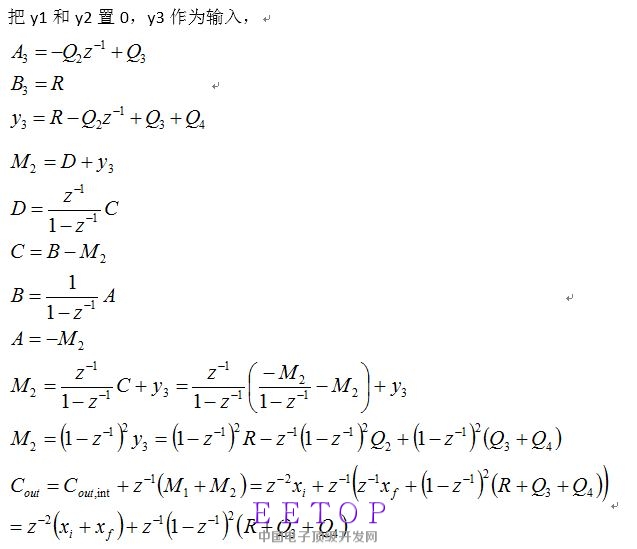

可以先把上图中来自小数部分的进位y1y2y3置0,这样可以推出来输出和输入FBdiv的关系是Y1=X1*Z^(-1),只是单位延迟。然后再把FBdiv置零,FRAC作为输入,最后肯定可以推出来Y2=X2*Z^(-1)+Qn(1-Z^(-1))^3,量化噪声是3阶整形。

总的输入就是Y=Y1+Y2了。

另外,反相器和进位输入置1其实是为了构造减法

多谢壮士拔刀相助,我按你的法子去推推看

你肯定是没看清楚,下面那个是两阶的,第三位是加随机数。另外里面有减法了就会推出来一堆项啊,不信你推推看呢

确实没仔细看,是2阶的。推出来被整形的不是加法器2的量化噪声,第一次见这种结构。

非常感谢!

直接加随机数的方法是不可能使用的,这样随机数的低频噪声全部在输出体现了。

直接加随机数的方法,是 dithering 吧,所加入的随机数总和为0,它能降低noise的影响。

我没有用过,不过paper上都这么说