chop +带隙基准仿真问题

时间:10-02

整理:3721RD

点击:

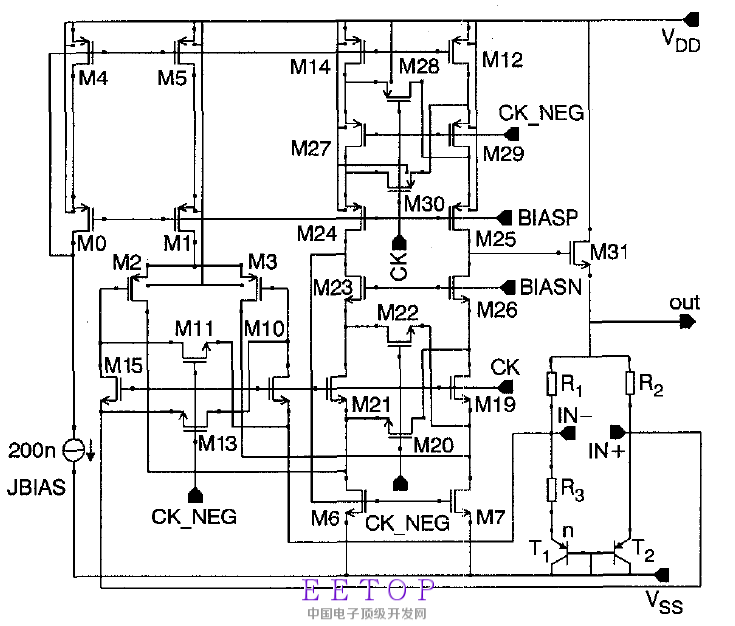

小弟目前在仿真一个带chop运放的带隙基准源,该结构如图1所示,

图1

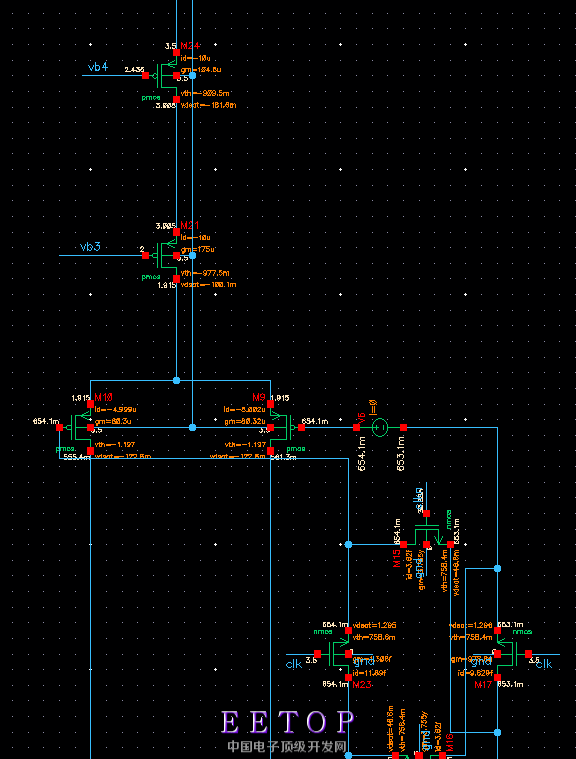

所有的直流工作点都正常,并且运放LOOP稳定。然后用理想的vpulse设计时钟信号,对其进行瞬态仿真,并在运放的输入端人为的加入失调电压

Vos=1m,如图2所示

图2

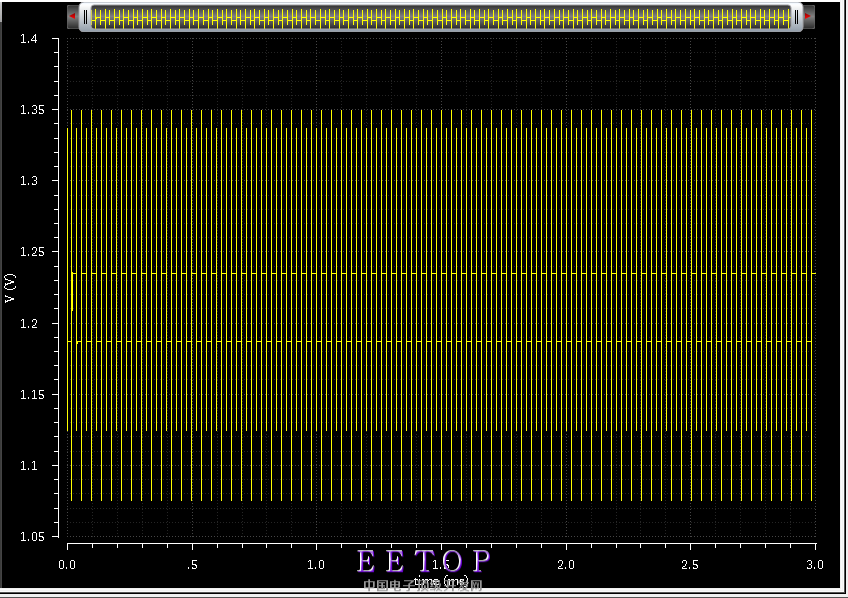

最终得到的输出基准电压如图3

图3

输出基准电压出现明显的矩形波形状,而不是稳定在1.2v附近,这里已经尝试过采用大电阻大电容作为低通滤波器,但是结果还是没有变化。

求做过类似chop电路的朋友们给予指导。在此谢谢啦!

LPF明显没有滤掉chop频率,要么提高时钟,要么狠狠滤波

带隙输出点处加R/C低通滤波器,效果并不是很好,并且论文本身貌似也没加滤波器。再则,有些不明白提高时钟频率的意义,还请麻烦点拨点拨?

chopper的输出没看到滤波啊。

chop频率太低了,没被bandgap loop 滤掉

那就必然看到方波喽。

低通滤波器的特征频率要低于chopper频率才有效果,从图片中看,是不是不满足这个条件?

是啊,出来就是个矩形波,难道需要在输出点加滤波器?

其实我已经将chop 频率增大了M级了,但是效果还是不怎么好。是不是需要刻意将loop带宽减小呢

chop的频率我已经给的很高了,达到了M级,出来后的glitch很大

1、如果没有加专门的低通滤波器,就意味着用bandgap的GBW滤波,bandgap的GBW是多少可以仿出来,一般在几百kHz级别;2、chopper频率即offset的载波频率,被低通滤波之后还剩下多少百分比,可以计算出来;

3、glitch是高频,由chopper的时钟引起的电荷注入和时钟馈通导致;解决方法书上有;

以上为个人拙见,仅供参考。

是的,问题基本上得到了解决,谢谢