pll不能锁定的问题

时间:10-02

整理:3721RD

点击:

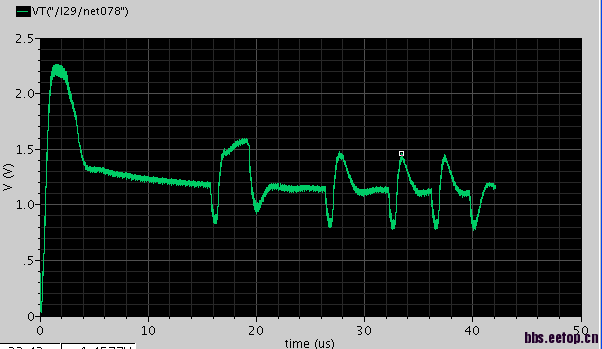

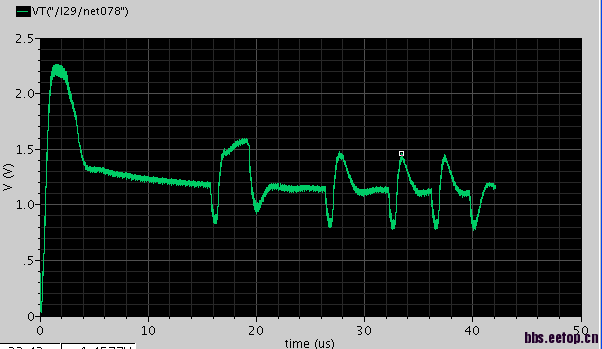

各位大侠好,小弟在做一个多vco的锁相环,即VCO分高、中、低三个频段,其他的PFD、div、cp、lpf共用。高、中频均可正常锁定,但低频锁定时的控制电压如下图所示,很是奇怪。难道是lpf的原因?但低频下相位裕度也有40度呢?求高手指教,谢谢

你的仿真精度是多少?maxstep?

谢谢您的回答。我直接设的moderate的defaults值,和这个有关系?低频是700M左右的,好像没必要吧,我换成maxsteps 1e-9试试,谢谢

check divider and pfd function firstly

40 degree is not enough

maxstep对仿真结果影响很大,本来锁定的,仿真结果却显示错误的。

一般maxstep设置为输出周期小两个数量级,你700MHz的周期为1.4e-9,所以maxstep顶多14ps,甚至更小,不过你高频却可以,这个我也觉得奇怪。有可能是楼上几位哥们提出的问题,嘿嘿

对了,还有从你图中看出,你控制电压的纹波好大啊,呵呵,可能是哪个模块没有设计好吧。

我说的不一定对,大家批评指正,嘿嘿。

谢谢,我也很怀疑这两个的问题,去check一下

是吗?倒真是低频的裕度最小的,也有可能,回去改改试试,谢谢啦

纹波可能是我改过一次lpf之后,R3选太小了,谢谢啦,解决后回来向大家汇报交流

看样子好像是vco或者后面的buf div之类的没有量化出来

我测试时也出现这种波形,但是相位裕度不是只影响稳定时间,只要相位裕度为正,就不应该出现这种情况啊?测试时相位裕度为10度时也可以正常锁定,难道非要设置相位裕度为60度及以上吗