1.2V的LDO设计问题

时间:10-02

整理:3721RD

点击:

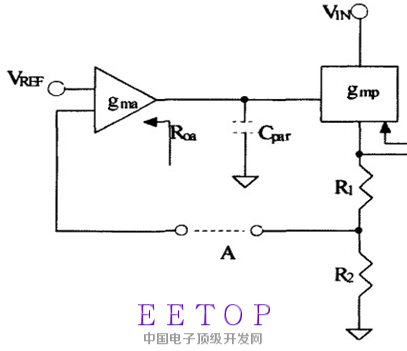

RT,想要设计一个输出1.2V的LDO,如果用1.2V的基准,可不可以将运放的反馈端直接接到LDO的输出(将传统LDO的电阻分压网络变成单个电阻),这样做会不会有什么问题?求大神们指点啊

比如VREF=1.19V,把R1做的很小,使LDO输出1.2V。

这样有什么问题么?

取决于性能的要求,如果驱动能力,瞬态响应等指标符合要求,这种设计就没有问题。

这样可以给数字电路供电么?

不可以。(1)驱动能力不够。(2)你这样设计最多最多只能叫做稳压器,不能叫LDO。如果运放的反馈端当做输出,Low Dropout Output在哪里体现?你可以产生一个低于1.2V基准,不一定非得用带隙基准啊。

学习了!

数字电路门数不多的话,没什么问题。

Low dropout指的是 input voltage和output voltage的差值吧,请教怎么不行了?

不多是指多少呢?

用1.2V做VREF LDO单位增益buffer 原理上一点问题都没有 但前提是ldo的性能要保证, 譬如精度要求比较高,一般都是通过修fb端的电阻,假如你基准出来的偏差了 并且没有trimming,那么这种流出来的精度就要差一些

可以,feedback factor=1,比较难stable。

数字电路多少合适,要根据你的实际电路的功耗和频率来分析了。你要确定你关注的指标是否满足要求,比如输出的纹波,驱动能力等指标。只要满足指标,数字电路门数再多都合适。

做法没问题,补偿可能不太好做

比如VREF=1.19V,把R1做的很小,使LDO输出1.2V。

这样有什么问题么?

这样设计相当于就是buffer了,频率补偿做好就行。