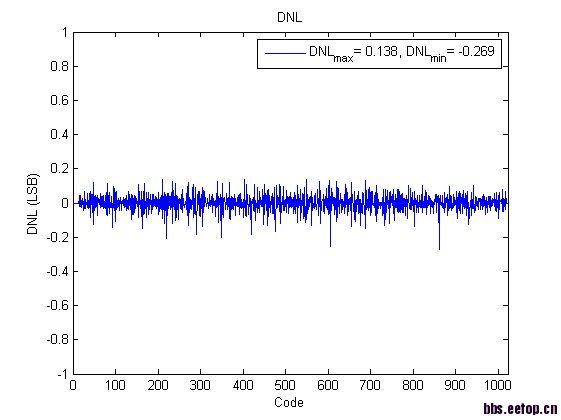

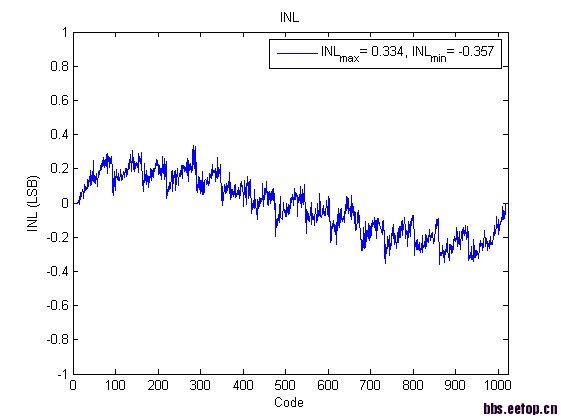

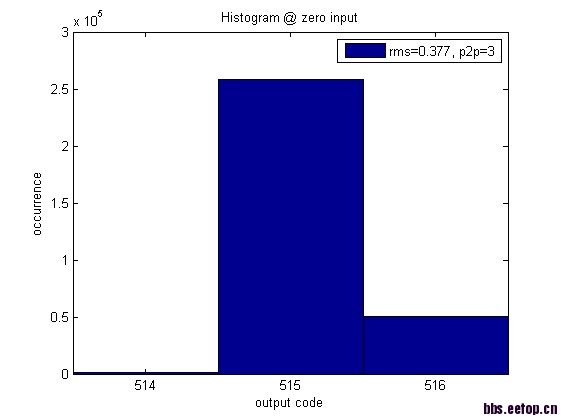

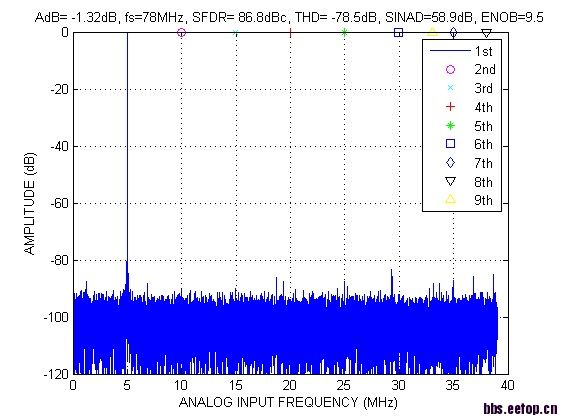

ADC的一点测试结果

10bit ADC的一点测试结果,65nm工艺,1.1V power,30mW,

1.5bit/stage,internal bandgap & reference buffer,无片外电容,

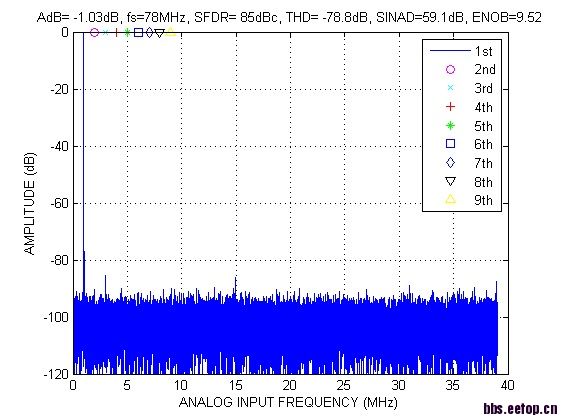

signal generator:agilent E4432Blogic analizer: agilent 16800 series

跟设计时理论计算及仿真结果比较一致,layout也是自己做的,比较优化,0.14mm^2

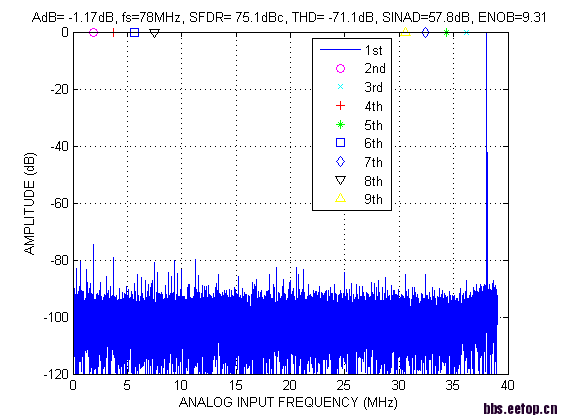

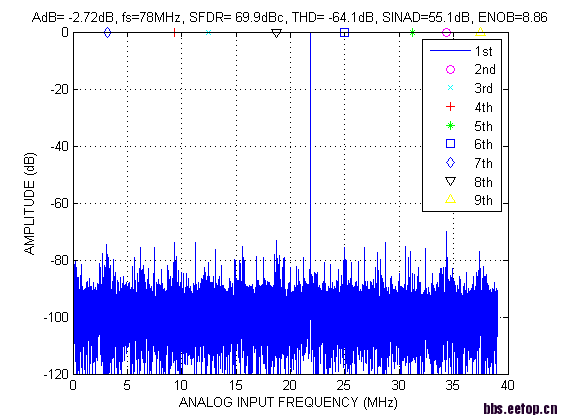

最后图片分别是78M sample rate,40M input signal, ENOB依然有9.3

100M input signal, ENOB 8.8

10bit ADC的一点测试结果,65nm工艺,1.1V power,30mW,

1.5bit/stage,internal bandgap & reference buffer

跟设计时理论计算及仿真结果比较一致,layout也是自己做的,比较优化,0.14mm^2

=======================================================

小编可以下山了,,,‘

1.5bit/stage怎解?

输入是1v额

输出vpp是多少?

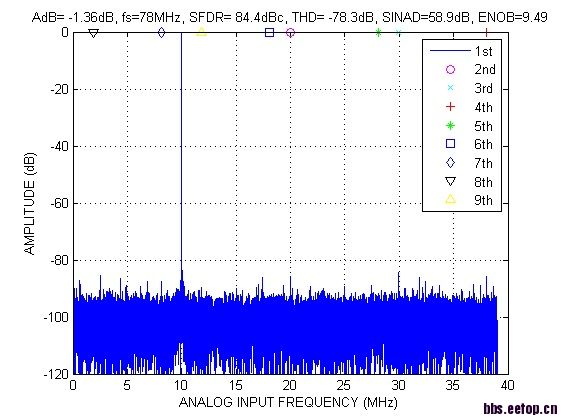

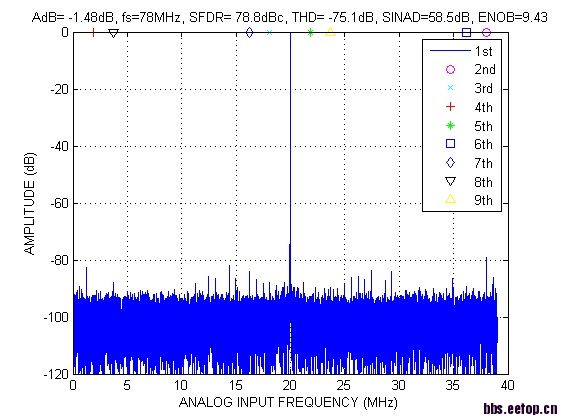

你看你测了10m和20m

你的最高输入频率多少啊。理论计算是怎么做的呢?

还有就是如何针对指标要求返回去计算OP的指标呢?

看了好多资料,说法都不一样。

tapeout后的测试结果吗?理论计算是怎么做的呢?

还有就是如何针对指标要求返回去计算OP的指标呢?

看了好多资料,说法都不一样。

tapeout后的测试结果吗?输入信号differential 1V,由内部的reference决定

比如0.3V~0.8V,内部每一个stage的输入输出都是这样

输入信号更高一点也测过,频率增加,性能逐渐下降多看看论文,国内论文不要去看了,多看看PR Gary和他学生的文章

自己多琢磨琢磨,要有自己的见解,就好了

以上都是实验室测试结果不错不错,是不是功耗大了点

不错不错,是不是功耗大了点

能做出来不错了,1.1v,30mw确实大了点,鼓励发多点信息,让大家多学习学习。

sampling rate 多少?

reference buffer 用什么样的结构?请问reference buffer 采用的什么结构?是外挂了电容的吗?

另请问测试平台采用的机器比如信号发生器的类型,时钟发生器的类型等,谢谢!无外挂电容的reference buffer

信号发生器agilent e4432B,逻辑分析仪16800系列我记得4432B的信号harmonic没有这么好,你在前面加filter了?

都要加filter的,包括e8663,信号源是要phase noise低,harmonic一般40~50dBc

好一点的能到60dBc以上,最好也要用filter看之前帖子不是设计250MHz?这个在接近nyquist频率下大概什么性能,有corner结果吗,用没有数字calibration之类的东西啊,给大家多提供点信息好让大家学习啊

这是100m的ad?有T/H么,考虑过jitter之类的么,是不是只有RSD,bandgap ppm能做到多少?我怎么感觉30mw功耗很低了呢,有人说高。而且从结果看,enob和线性度很高啊,了不起。还有就是65nm下,理论计算用的是什么模型,听你说与实测结果相一致,那不会还是二次方程模型吧?

顶起学习!大侠多放点毒嘛,比如什么结构,参考资料等等....

同感,sampling rate是78MHz,相比之下不到30mA的电流,功耗控制已经很不错了。说功耗高的人做个15mA的来看看,光说不练假把式。

BTW,建议小编分享一些做项目中看过的觉得不错的ADC论文,让大家也学习学习。filter用什么型号?

如果输入信号到39M还是不错低,可是这个只有20,所以功耗得按20算,我还真做过只有10几毫安,差不多的性能,不过40nm

同意16楼的观点。

从线性度上来看都能到12bit的指标。算了下fom大概0.53pj/conv,很强。另外如果片外无电容的话只能片内高速buffer了吧,这都能把功耗控制到30mW...反正我觉得太给力了。

另外20楼的话,40nm下做的是什么结构的AD啊?不知道你这个0.5pj/conv是怎么算出来的,输入信号只有20m,fom只能按40m算

我是新手,也在学习中。那么你的意思是fom的计算必须用乃奎斯特采样的情况计算?

要不然我用over sampling 不是可以作出非常好的fom

最后一张图片是78M sample rate,40M input signal, ENOB依然有9.3

其实这是一个200MHz 10bit的ADC,只是在测试的时候有些奇怪的问题,所以暂时跑一个较低的频率罢了

78MHz是板子上156MHz oscillator 的分频

在跑156MHz sample rate的时候,噪低会起来,但不是谐波,是所以频点上都会有,而且间隔也比较固定

怀疑是哪里couple进来的干扰,性能不那么漂亮,也就不贴出来了说的是,不过比较FOM的话你总不能拿NQ ADC和OS ADC比吧。但是如果都是乃奎斯特AD的话,我觉得即使是低频信号,也是有一定说服力的吧;当然了,如果做得不好,高频输入也会衰得很厉害,但是lz这个片子我觉得采40M信号应该不成问题

如果你测用100M+的采样率测高频信号的话,oscillator应该已经不给力了,可以试试直接使用更好的时钟源。另外很想了解下参考buffer的结构~

reference buffer 我用高速opamp,也可以用replica source follower

小编你的整个reference的架构是怎样的? 是regulator电阻分压后接unit gain buffer做ADC的reference驱动吗?你的高速运放的功耗是多少?

reference buffer 如果是高速opamp的话,是differential结构还是用两个single ended?另外,你用的是什么类型的电容? mom还是mim?第一级采样电容有多少?

你刚才提到采样频率上去了就有些问题,我建议你用单独的low jitter的源做时钟然后和你的输入信号源syc起来,这样可能会有改善。