一个关于PLL时域行为模型的相位噪音的问题

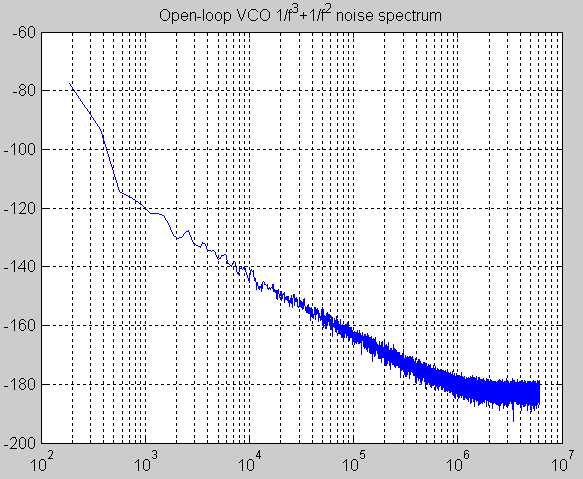

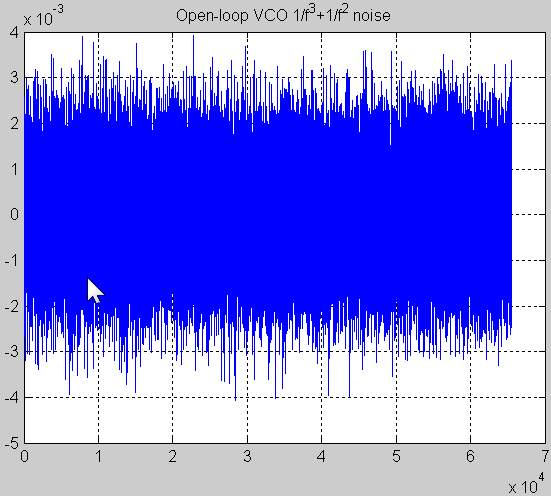

我刚用MATLAB写了一个PLL的时域行为模型,里面加了(开路)VCO的1/f^3+1/f+白色时域噪音如下:

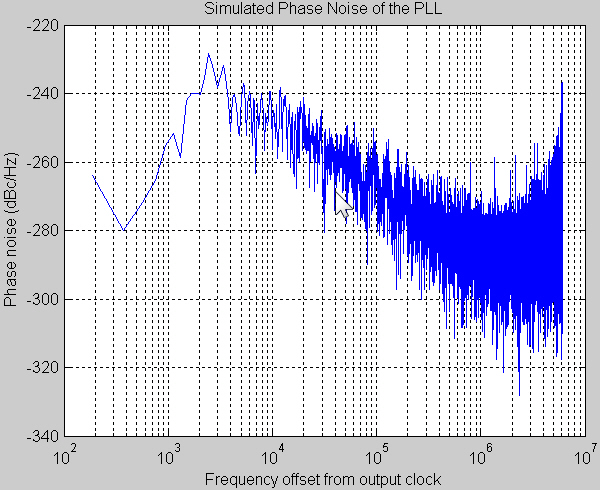

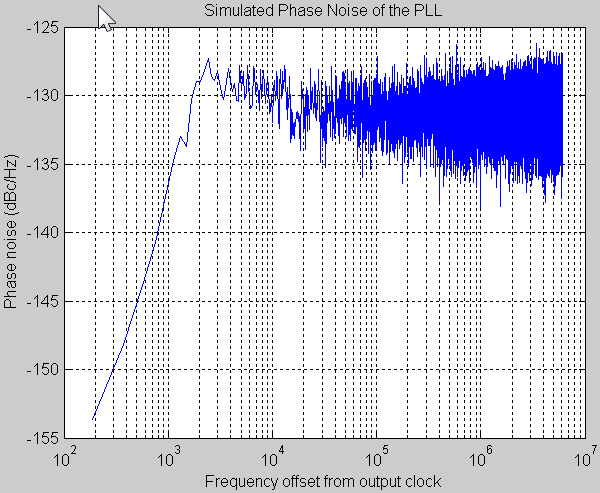

在PLL的时域行为模型里,我用如下方法将此噪音加到了VCO的输出上:判断VCO的输出相位是否在此计算时间经过0或2*pi(或其整数倍),若是,则在VCO输出的相位上加上此噪音。这样作后,PLL的时域行为模型的相位频谱输出是:

可以看到(开路)VCO的高频噪音基本上直接显示在了PLL的输出上,而其低频的噪音得到了PLL回路的抑制。

现在我的问题是,此PLL模型的其它部分我都用开关设成了理想状态,当将此VCO也设成理想状态时,PLL输出的频谱非常干净(即没有上图中的spurs)。且若我将VCO的噪音改为只是白色噪音的话,PLL输出的频谱在高频也显示出了那些白噪音,但没有上图中的spurs。但不知为什么VCO加了1/f^3(或)+1/f噪音后,这些spurs就显示出来了。图中最低频的spur是在PLL的输入参考频率,其它是它的整数倍。

我想可不可以这样解释:VCO加入1/f^3(或)+1/f噪音后,因其是非常低频(DC)噪音,这样PLL的电荷泵(charge-pump)就需在每一输入周期用一几乎相同的、多余的差分脉冲来纠正此一DC噪音,这样就像由于电荷泵正负电流匹配误差引起的参考时钟泄漏(reference leakage)的效果一样,也会在PLL的输出产生spurs?

诚望高手予以解惑!

VCO有1/f噪声之后,你的feedback divider实际上就相当于对VCO的频率进行积分,而VCO的频率这时候可以看做是一个变化的量,当divider除到输入参考频率的时候,就会产生一定的相位差。但是如果你用白噪声,如果divider的数值够大,除过之后的噪声被平均掉了,和没有噪声是一样的,因为白噪声的均值是0。是不是可以这么理解。

谢谢答复!和我的理解类似。觉得根本原因是由于VCO的1/f低频噪音引起的DC偏执(bias),每次divider除到输入参考频率的时候,所产生的相位差大都具有类似的极性(polarity),这样就会leak到charge-pump一个具有参照时钟频率的分量。

VCO加了1/f^3(或)+1/f噪音后PLL就显示出spurs,这正不正常?还是model的问题?

不知道你的模型能看静态相差么,如果没有很高的要求,静态相差只要小于输入参考时钟的千分之一就行了。通常情况你这个VCO引起的静态相差要小得多,电荷泵失配和PFD消死区的影响比这个更大。如果单纯VCO引起的静态相差就很大了,那可能是你加噪声的点的问题

你说的“静态相差”是什么意思?(英文?)是指在没有任何非理想性的情况下的相位噪音吗?下图是我的模型给出的理想状态下PLL输出的相位频谱:

可以看到此时相位噪音非常低。我用这一输出时钟去采样一理想信号(大约100倍过采样oversampling rate),结果给出了186dB的信噪比(SNDR)。

你提到可能是加噪音点的问题。我读过几篇这方面的文章,大部分也是将VCO相位噪音加到了VCO输出上,只不过他们是持续加的,及不像我的一样是在上升沿的zero-crossing时才加。我觉得不应持续加,因首先你从spice模拟得到的VCO的相位噪音只是反映了时钟在上升(或下降)zero-crossing时的时间不确定性;其次,不管在其它时间PLL回路中有什么噪音,只有当VCO的时钟在上升(或下降)zero-crossing时的时间偏差才算数。也有的是加在VCO控制电压上,但我觉得那样更不靠谱。

静态相差是static phase error, 这个PLL都会有,就是补偿你前面说的电荷泵失配的。是指PLL的参考时钟与反馈时钟之间的相位差。感觉你加噪声的方法是可以的。

你可以人为的把电荷泵的充放电电流调失配了,不加噪声也能看到spur。要想把spur减小,就要用更高阶的滤波器,4阶滤波器可以,但是这时候要注意环路稳定性,大概40度的相位裕度就可以了。

如果你单加1/f形状噪声在VCO输出,也有这个spur吗?

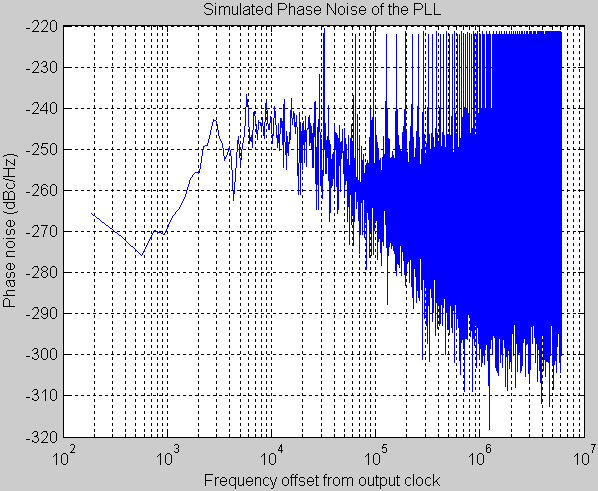

谢谢回复!对,只加1/f噪音也会产生那些spurs(当然幅度不一样),只有VCO若是理想的,或白噪音情况下那些spurs才会消失。另,下图是我若其它所有block都设成理想,只是在电荷泵加了1%的失配所产生的PLL输出的相位频谱:

刚更新了插图。

你确定,其他模块理想时,vco输入端的白噪声无spur?

确定。这是只有VCO有白噪音时PLL输出的相位噪音图。

请问你的白噪音加了多大?我觉得spur太小淹没在noise中

vco input reference和vco输出 pnoise转换你是否知道?

谢谢回复!我又把白噪音加大了好多,如下图,VCO开路cycle jitter大约20ps左右

PLL输出中没看到明显的reference spur (32kHz)

我相信上图中准也会有被埋没的reference spur,毕竟白噪音也有低频分量。但若被埋没了,那么相对来讲就不重要了。你说的vco input reference和vco输出 pnoise转换是指什么?

您好!请问您时域模型怎么写的呢?是even driven model 吗?时域的model怎么加入噪声呢